【嵌入式Linux】---- 基于VIVADO新建创建硬件描述文件(hdf文件)

基于vivado创建hdf文件

开发板芯片型号:ZYNQ7010

vivado版本:2018

功能:Flash烧录、串口通信、网口通信

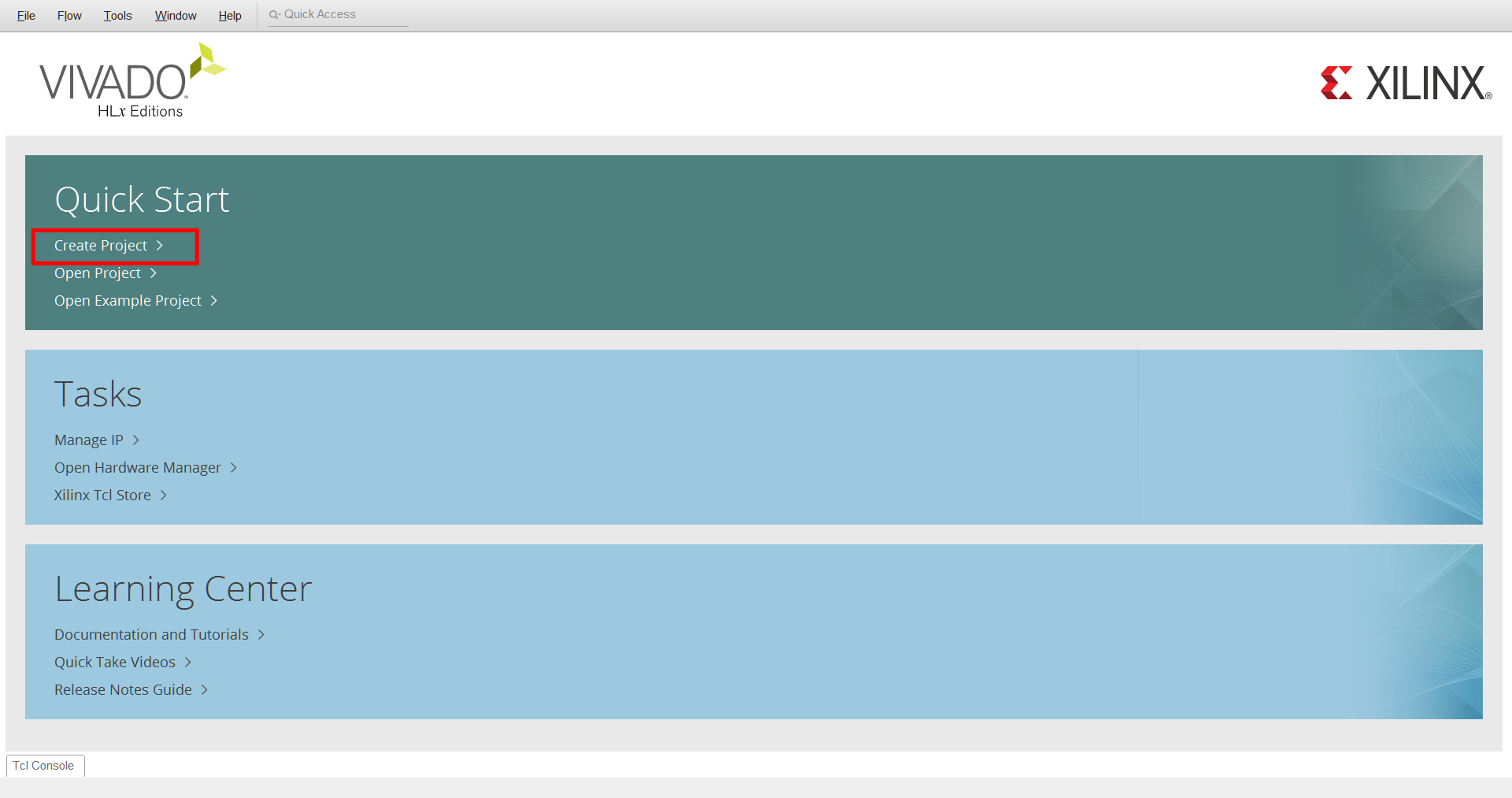

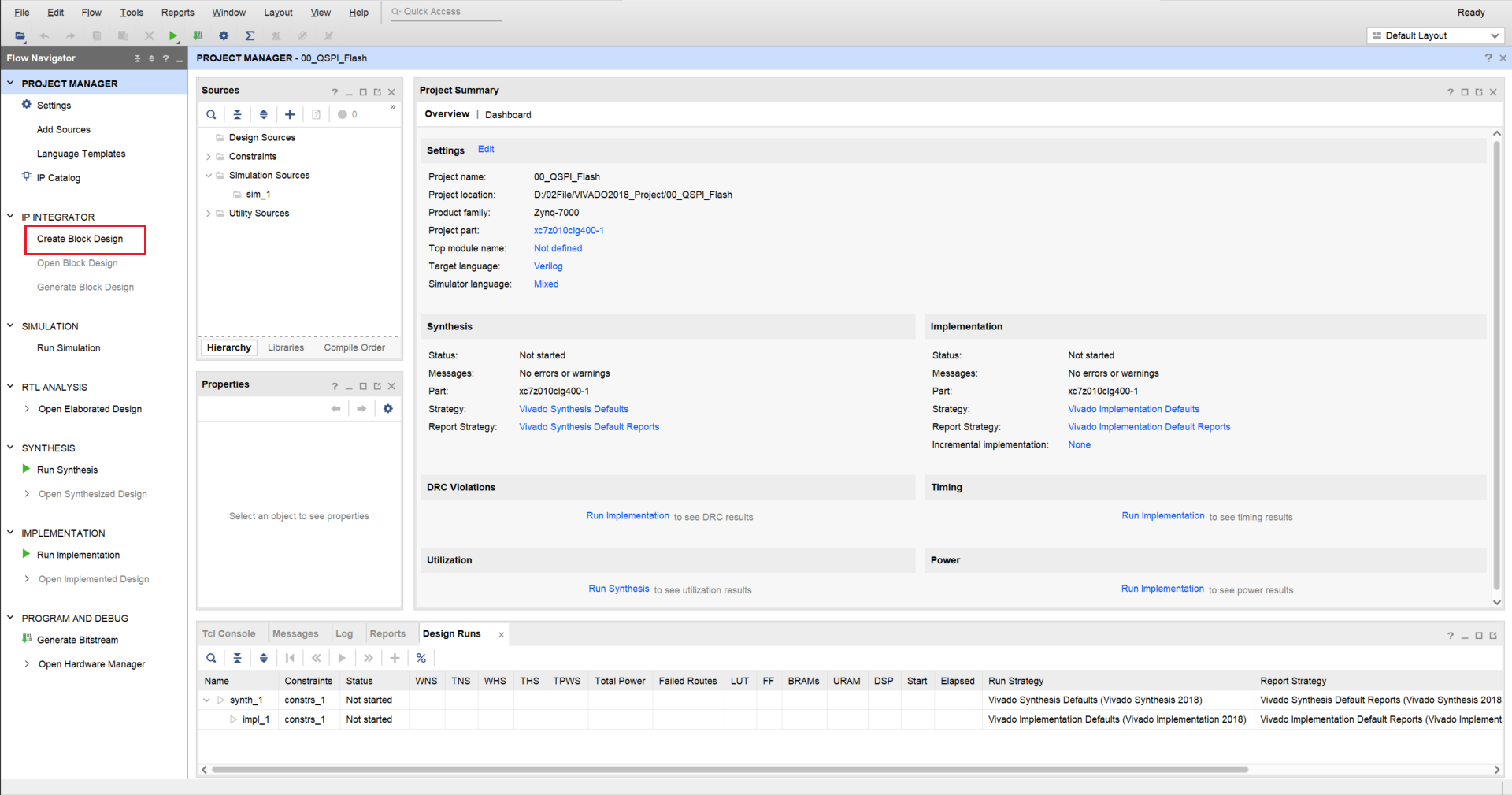

1 基于VIVADO创建工程

打开vivado软件,创建工程

点击NEXT

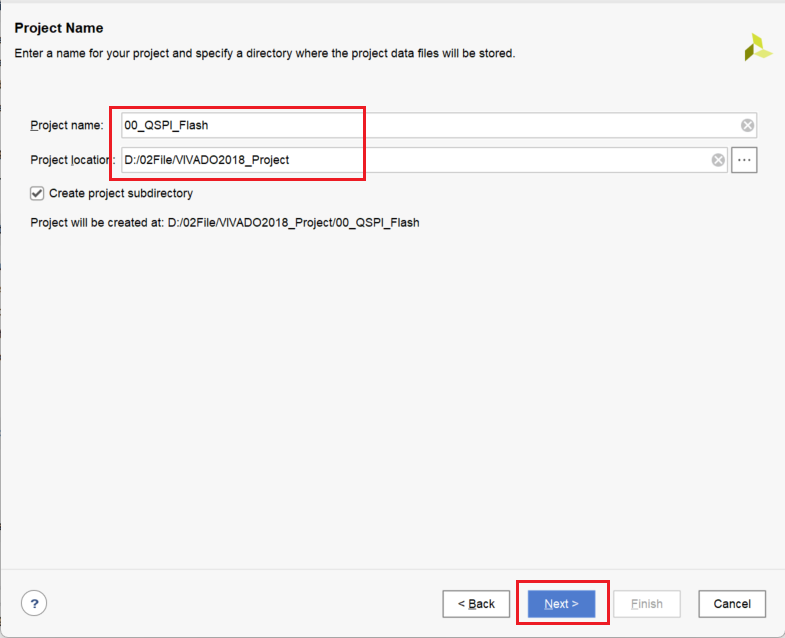

工程命名和选择工程存放路径,然后点击NEXT

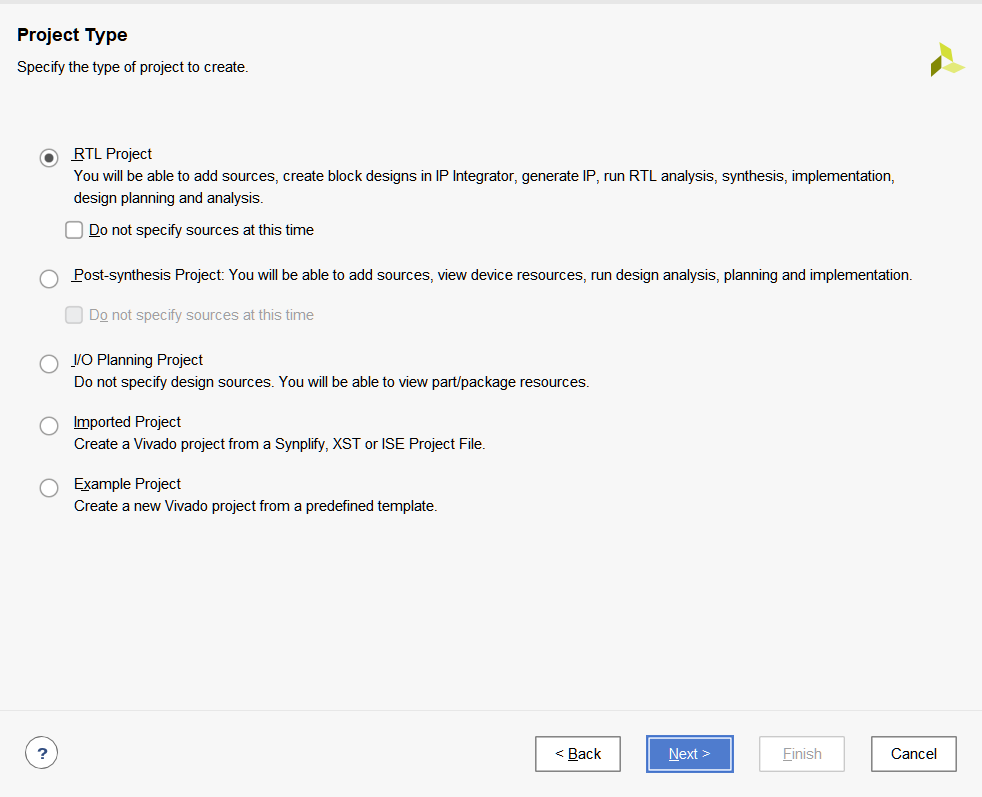

文件类型,默认即可,点击NEXT

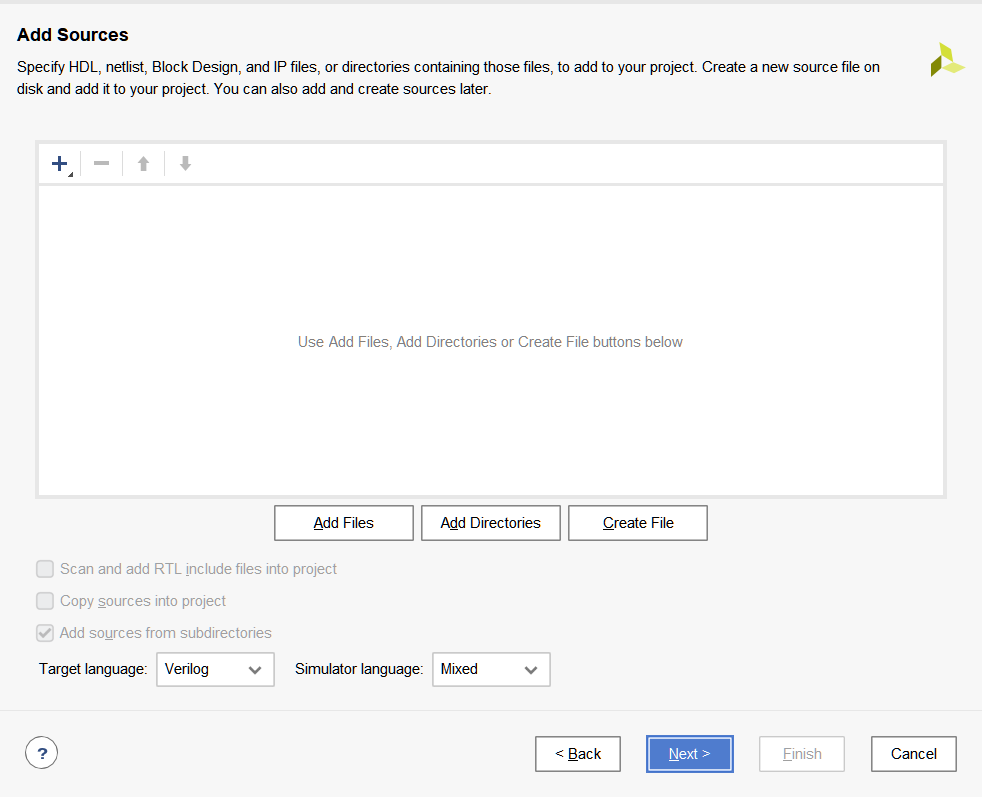

添加源文件的界面(如果自己已有源文件,可自行添加),没有源文件就直接点击NEXT

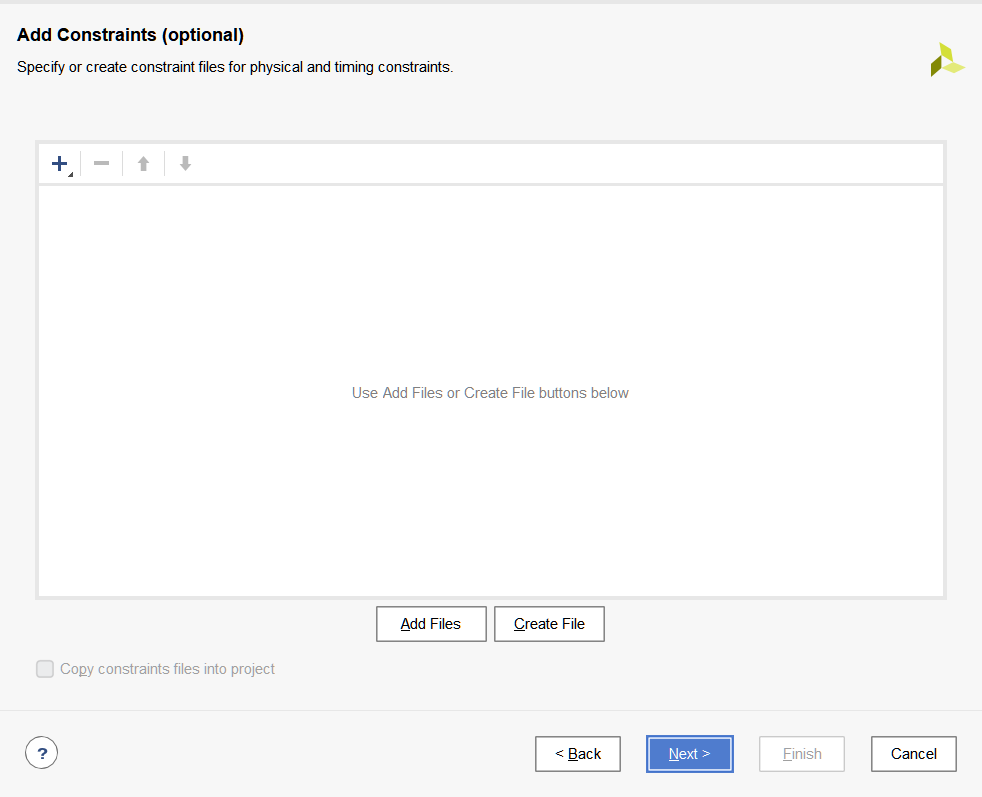

这里是添加约束文件(包含管脚配置、电平标准等),没有就直接NEXT

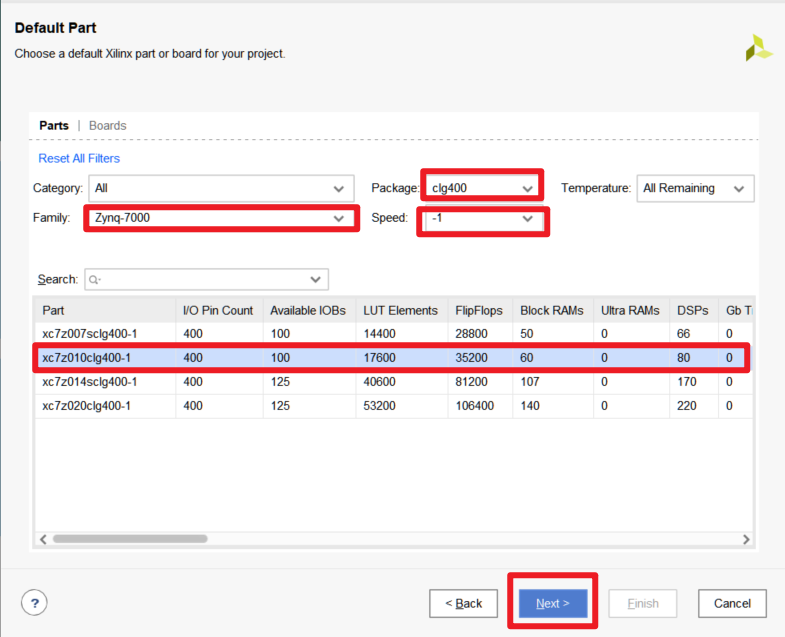

然后根据自己的开发板选择对应的芯片(在速度栏中,7010的芯片选择-1;7020的芯片选择-2),再点击NEXT

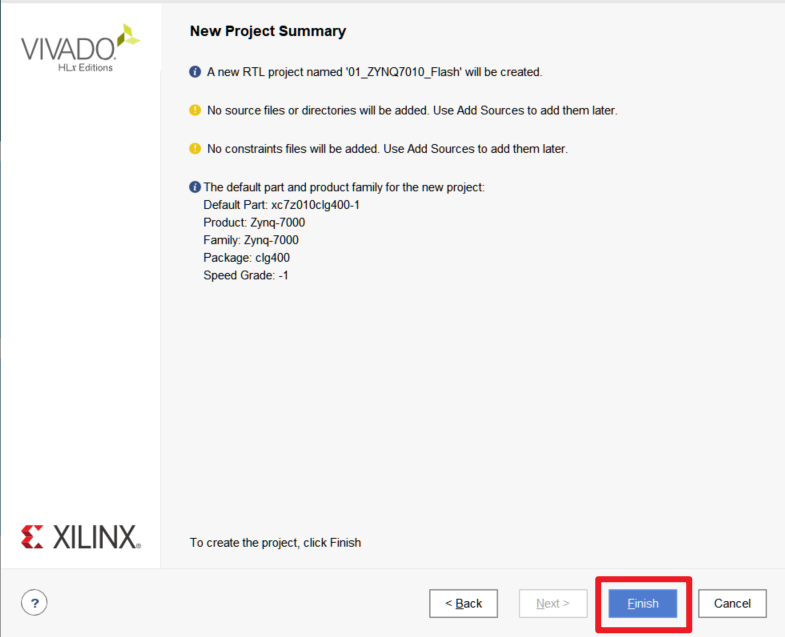

检查信息,确认无误后点击Finish即可

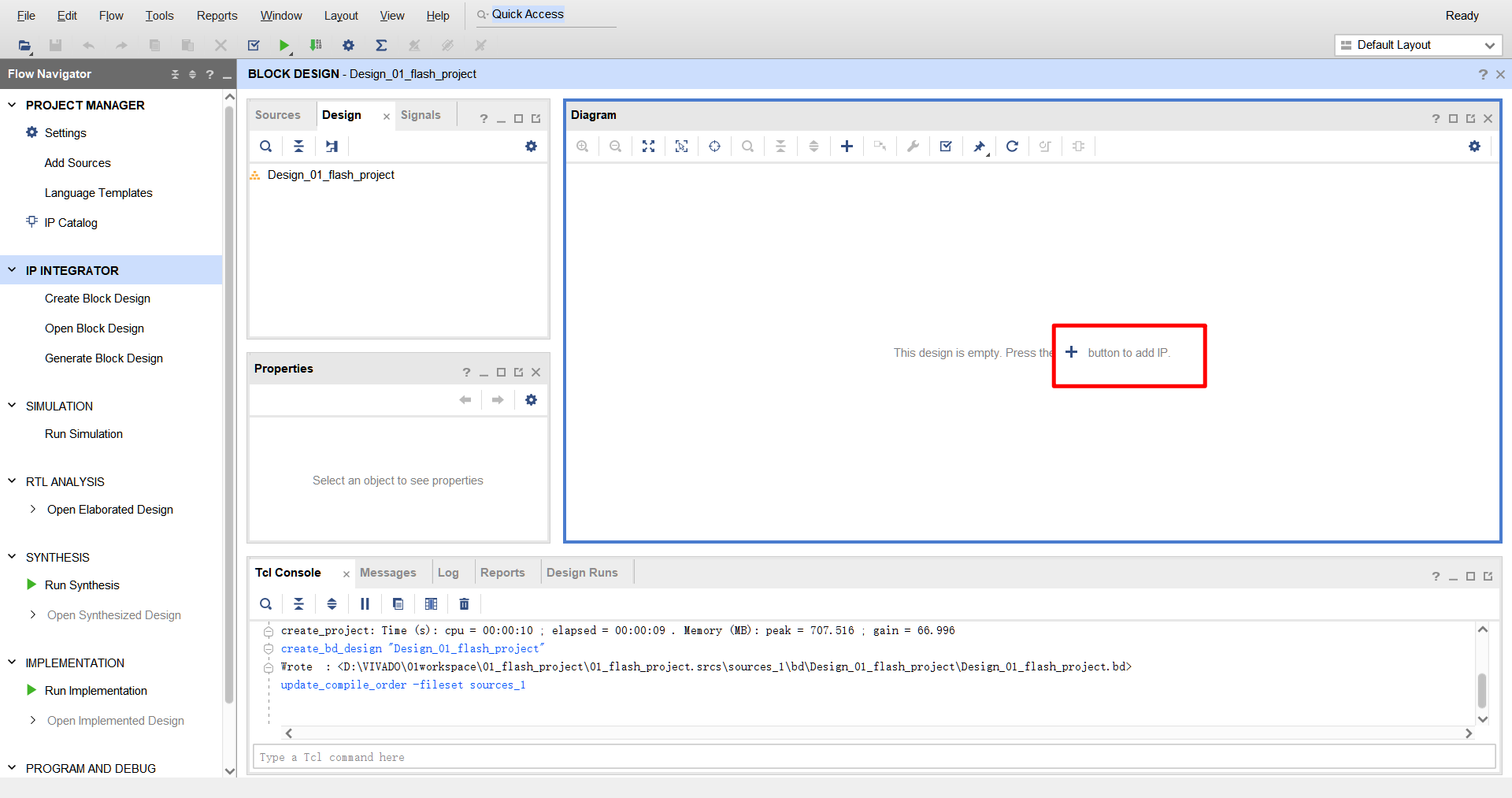

2 创建设计

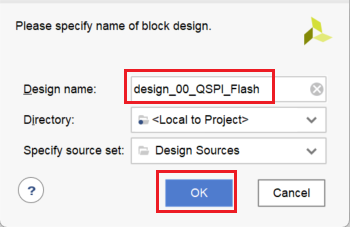

点击Create Block Design,

输入工程名称,然后OK

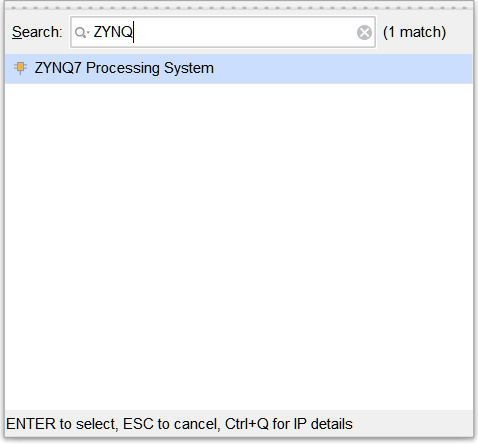

添加处理器内核

输入ZYNQ,然后回车

双击芯片,进入功能设计界面

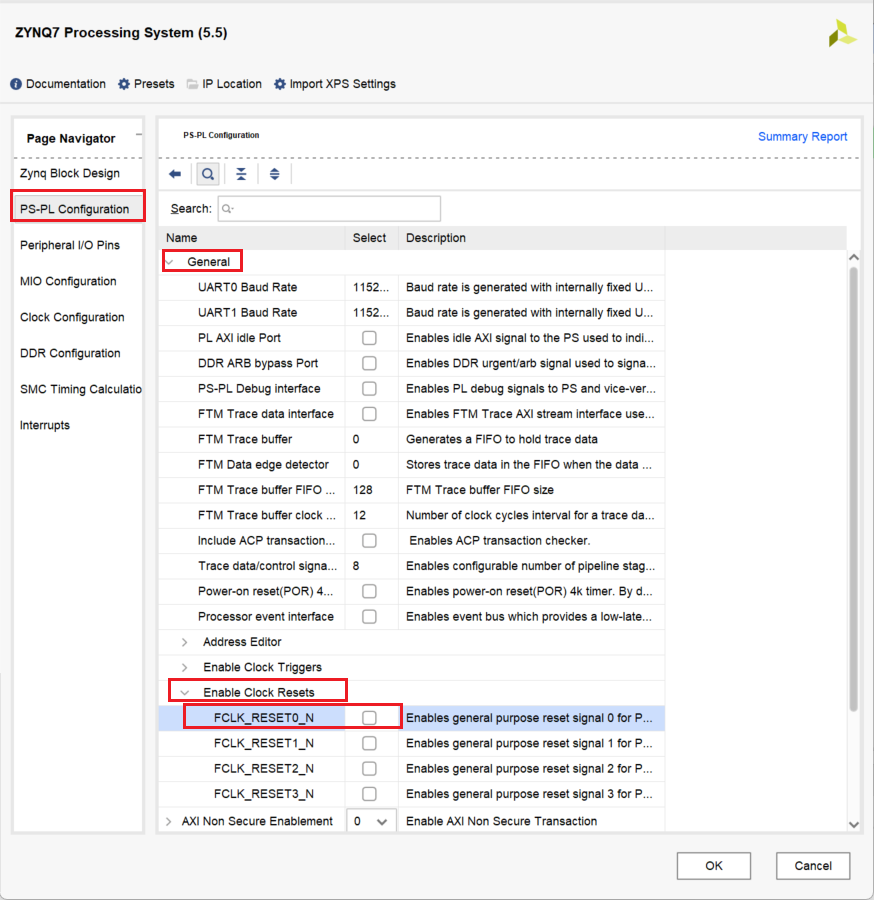

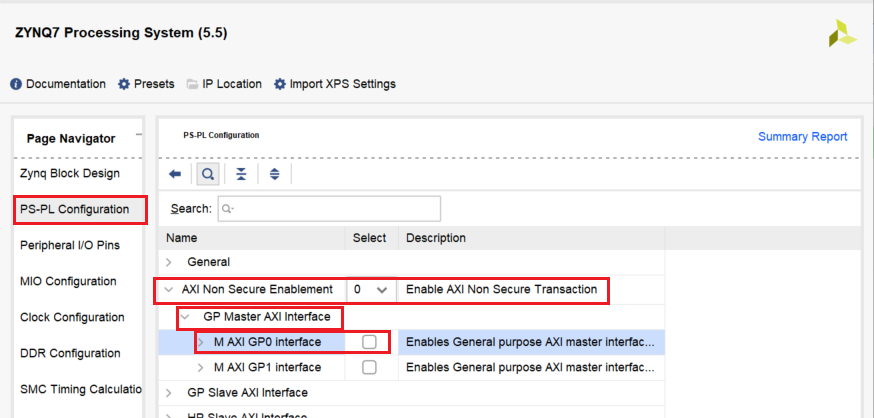

2.0 关闭PS-PL端交互接口

取消FCLK_RESET0_N的勾选

取消M AXI GP0 interface的勾选

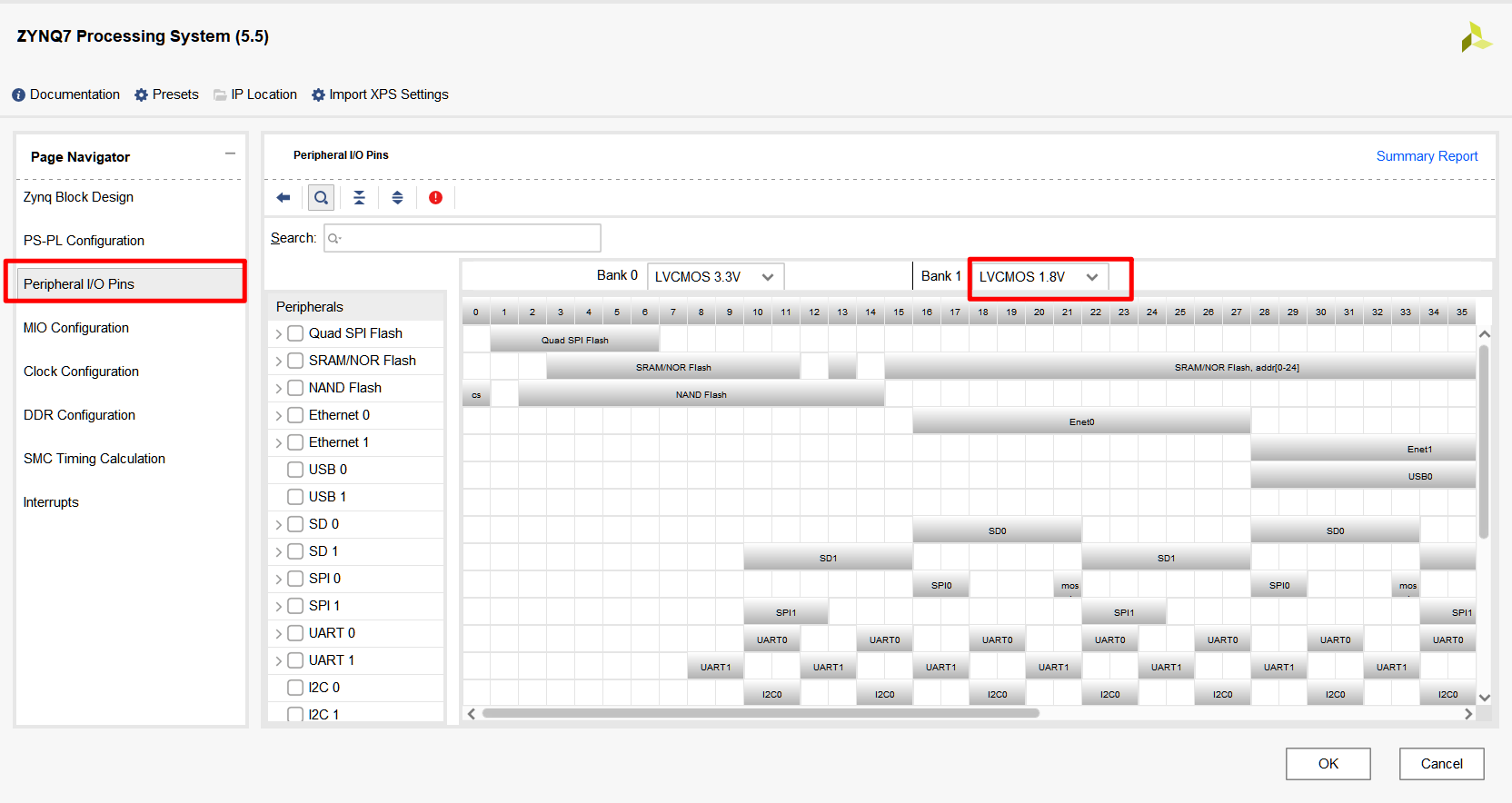

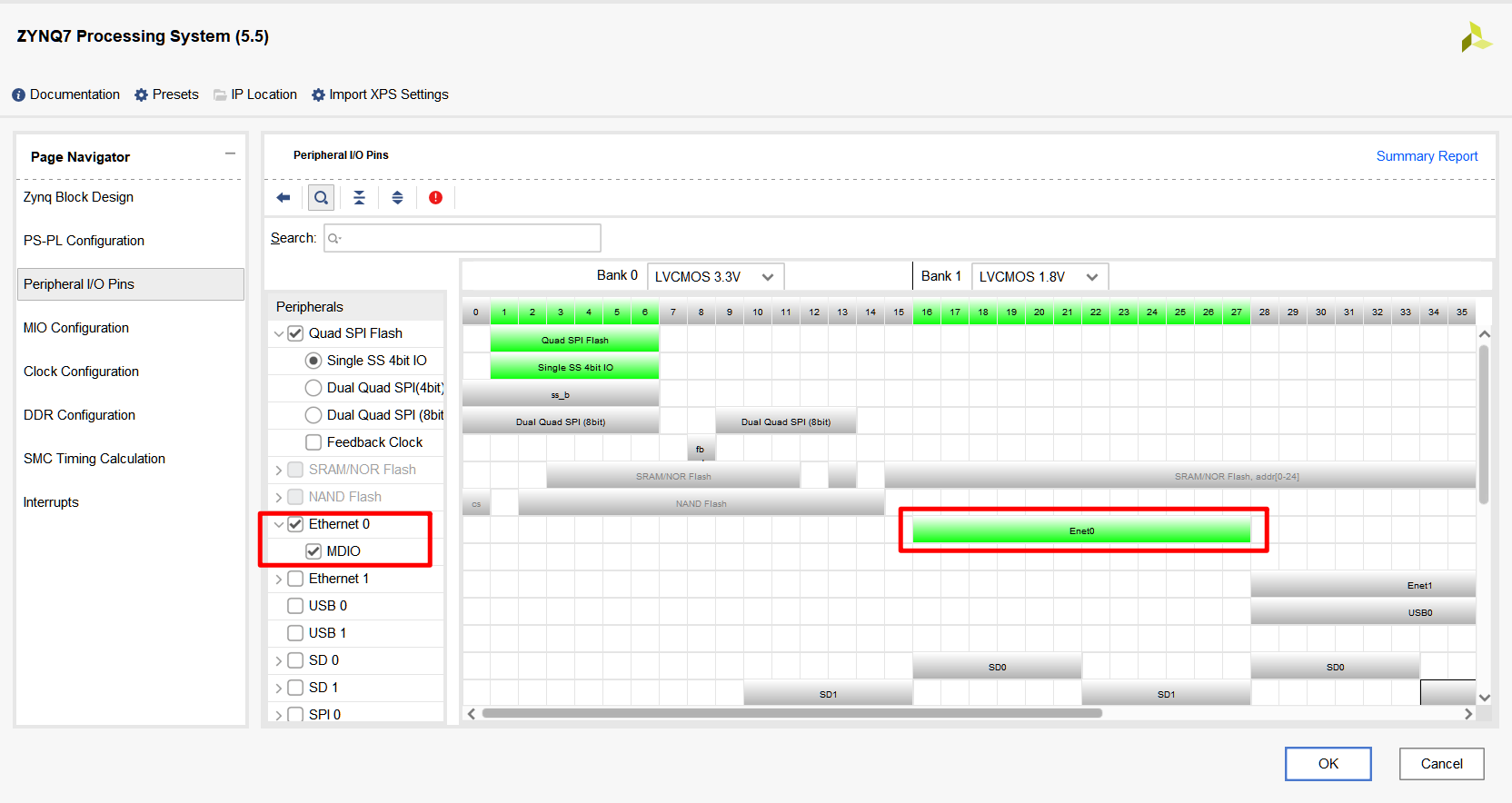

2.1 配置Peripheral I/O Pins

在I/O引脚设计界面中,将Bank 1电压设置为1.8V

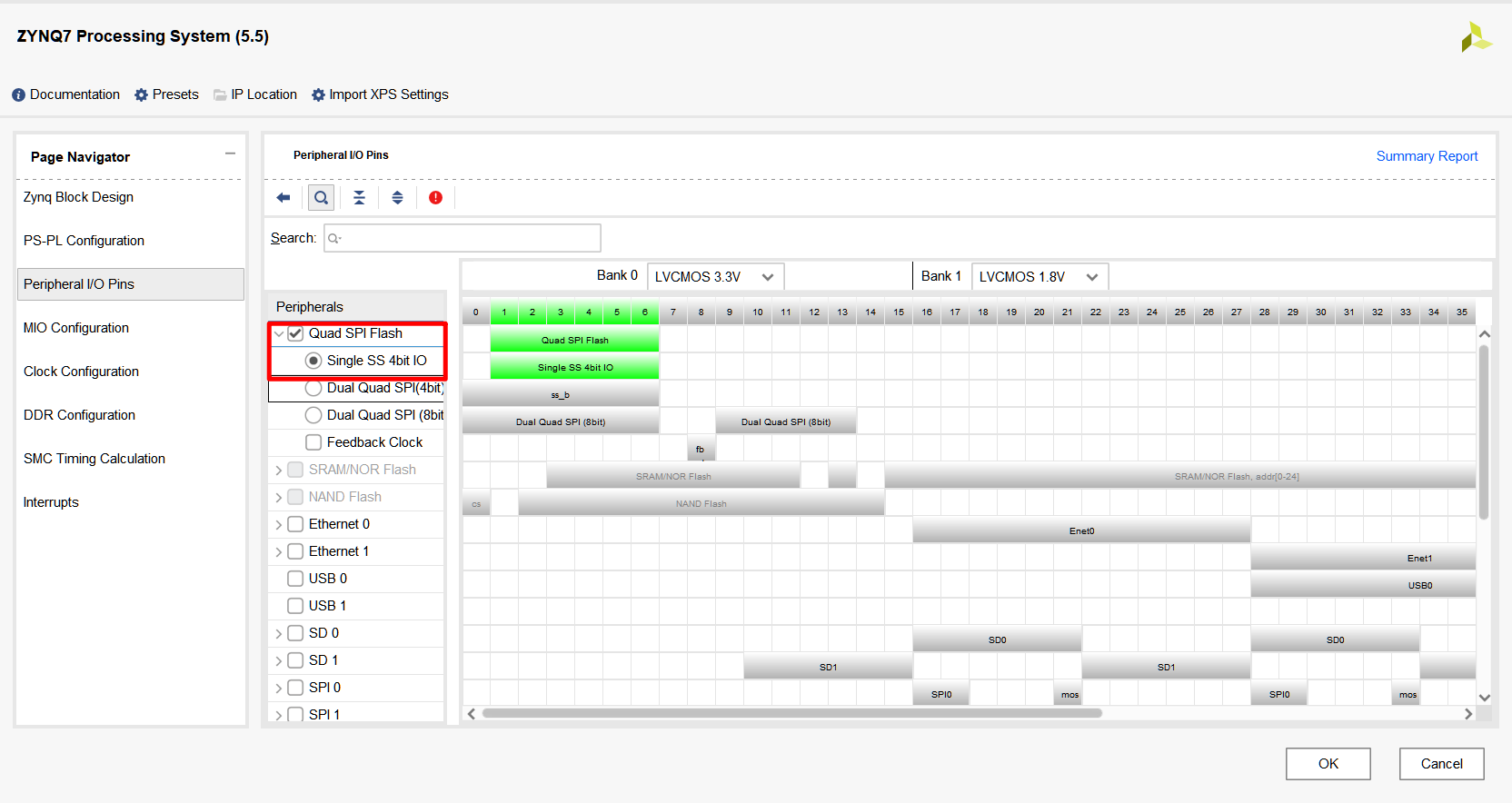

然后使能QSPI Flash

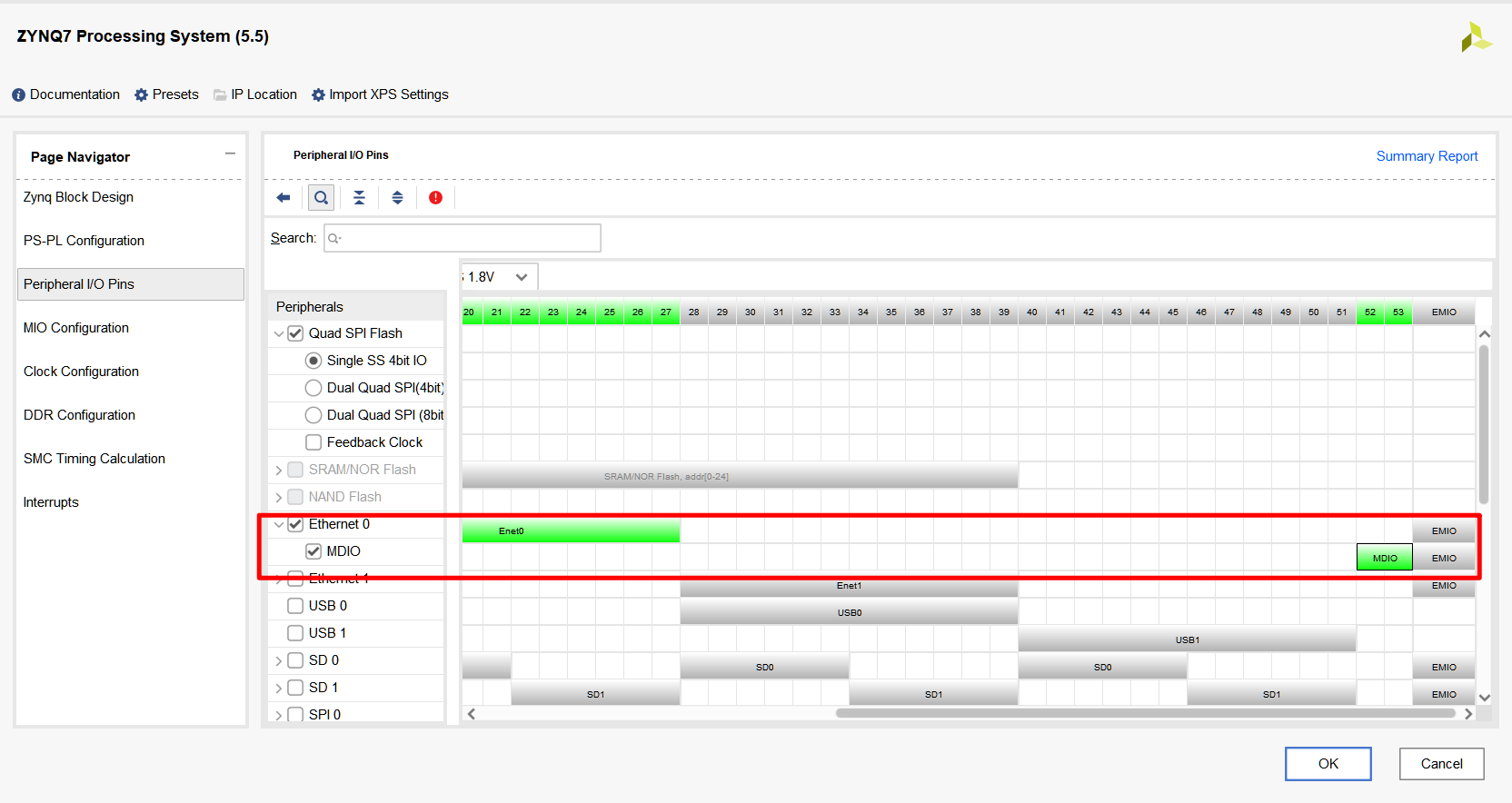

鼠标点击Enet0,使能Ethernet 0

同时,右拉进度条,点击MDIO进行使能

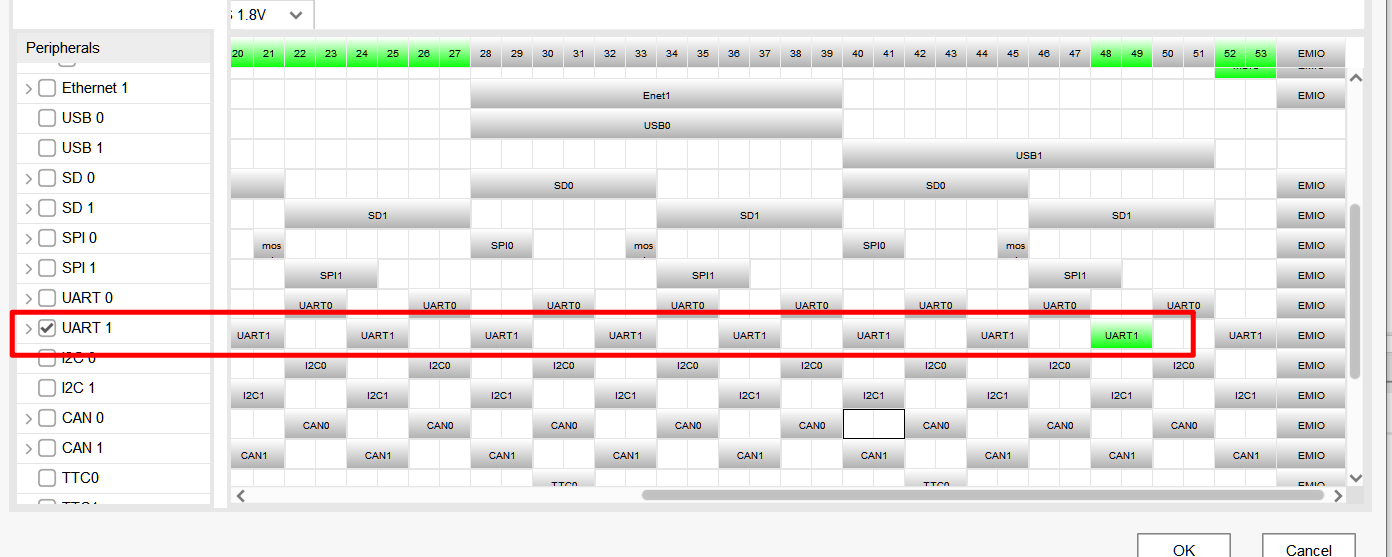

再使能串口UART 1

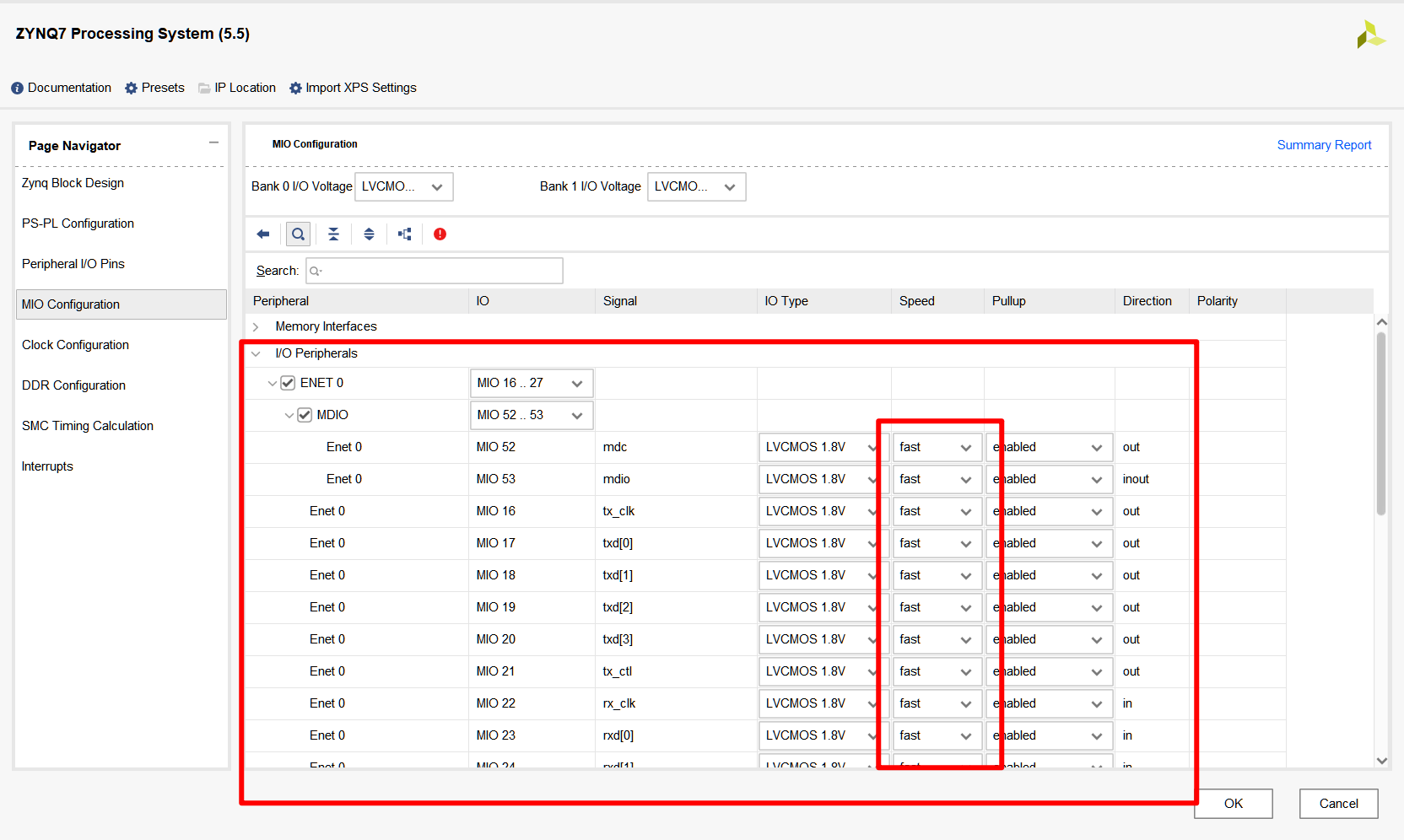

2.2 配置MIO Configuration

修改QSPI Flash接口引脚的速率

修改网口Enet 0的速率

2.3 配置Clock Configuration

取消FCLK_CLK0的勾选

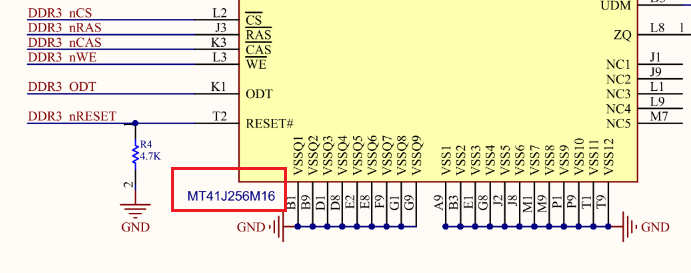

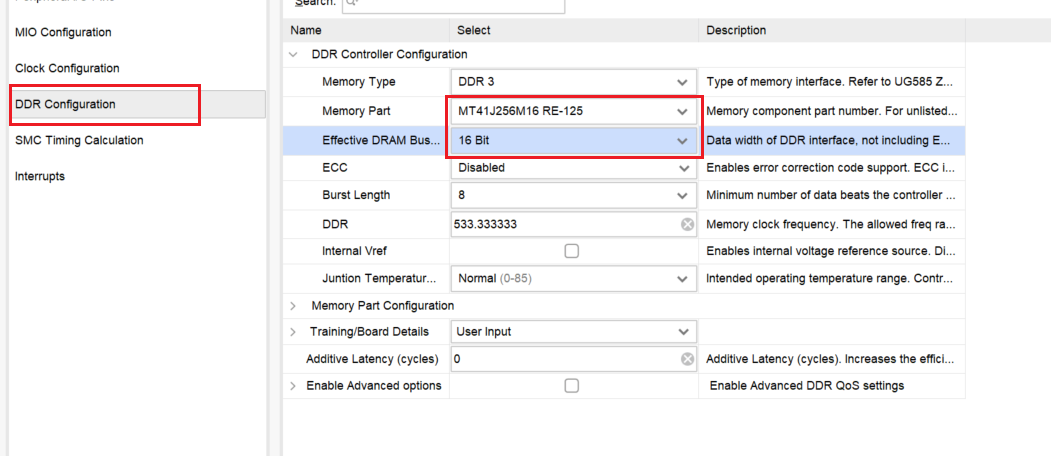

2.4 配置DDR Configuration

这里DDR里的 Memory Part参照开发板上的存储芯片的具体型号

位宽选择16位

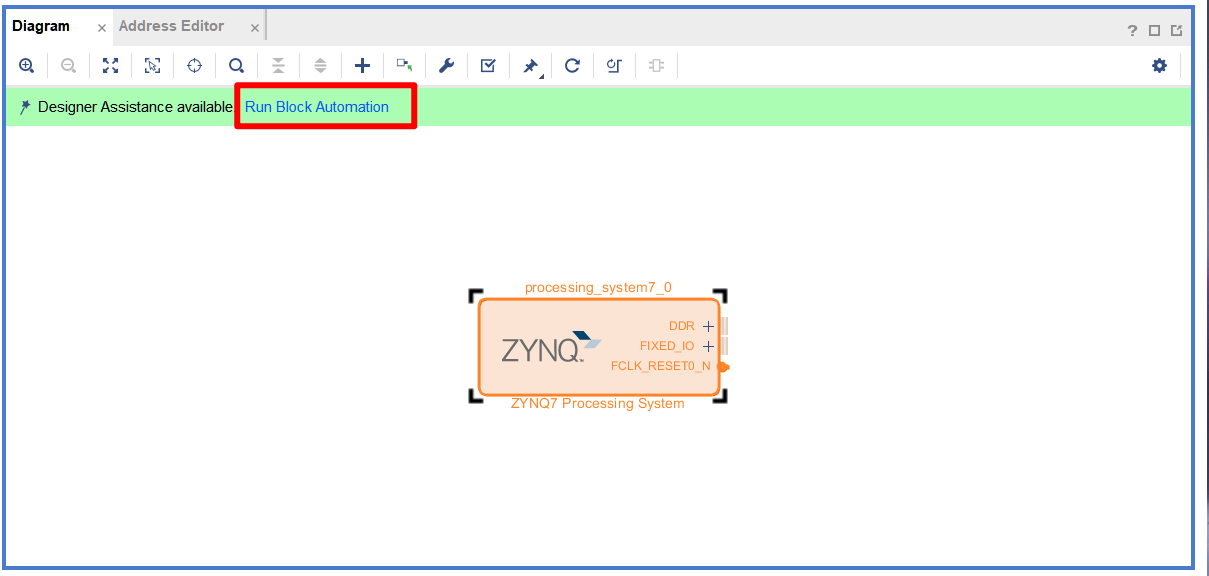

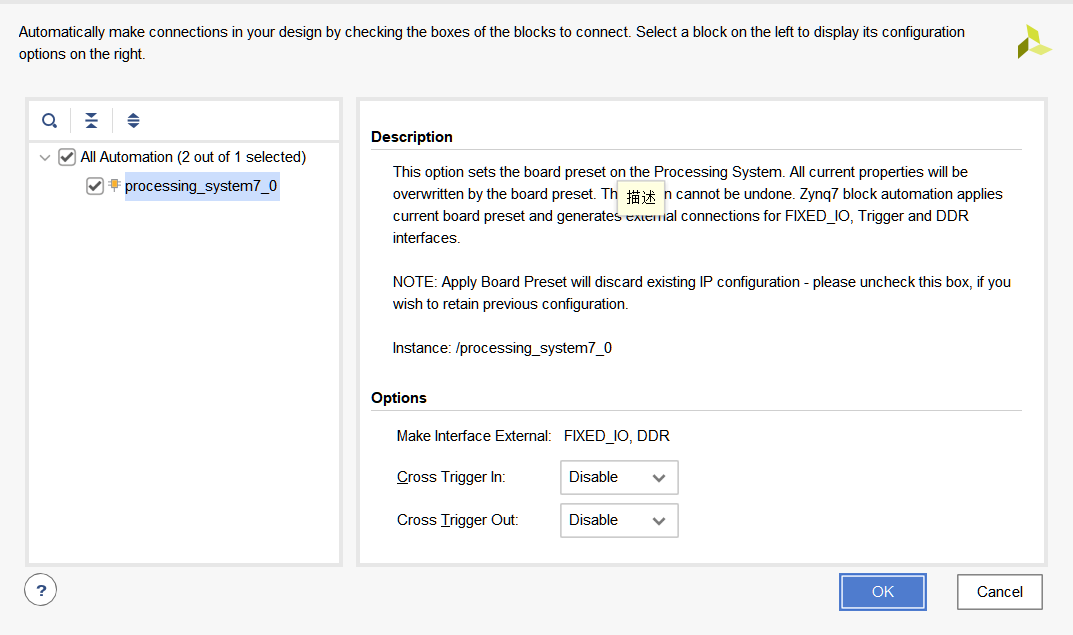

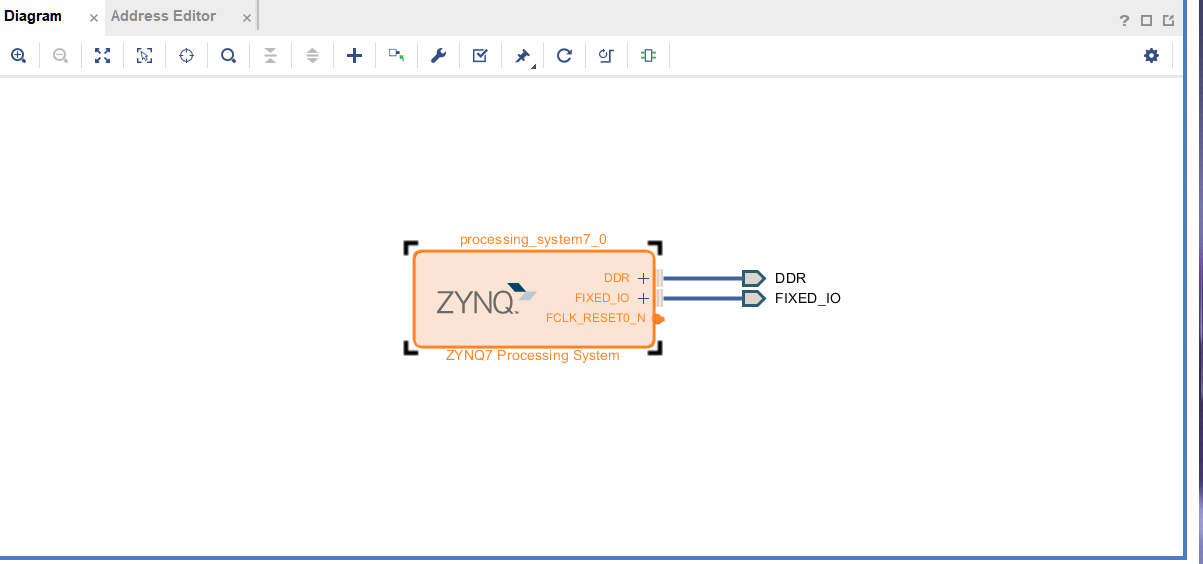

设计结束,点击OK,关闭设计界面,点击Run Block Automation,引出管脚

点击OK

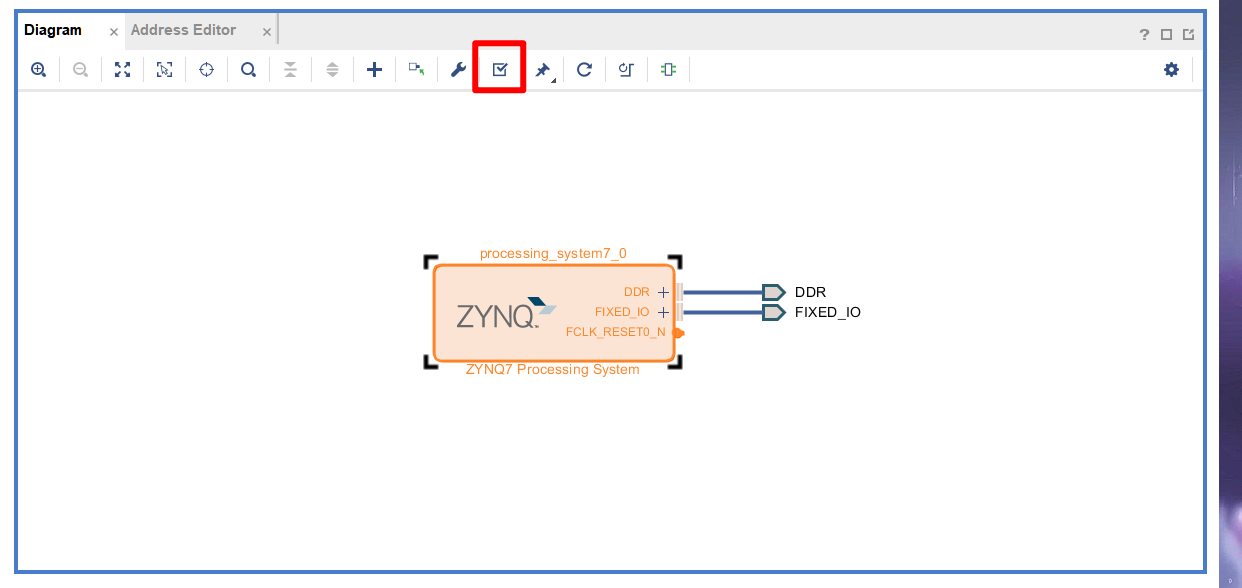

3 验证设计

无报错,点击OK

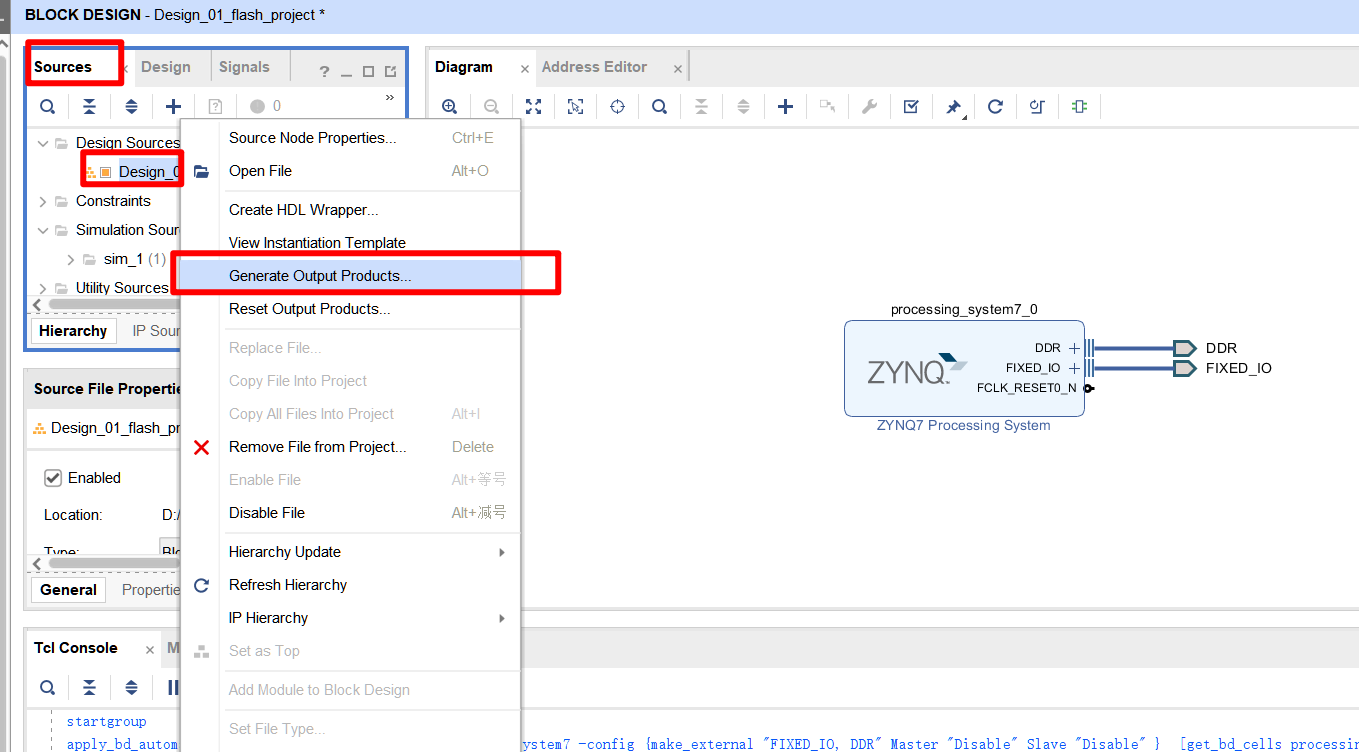

4 输出文件

然后点击Generate,等待生成即可

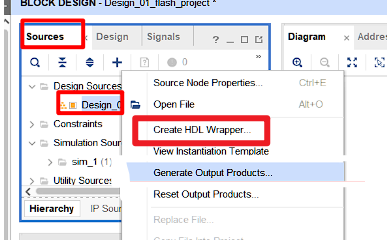

接下来生成HDL文件

直接点击OK,等待生成

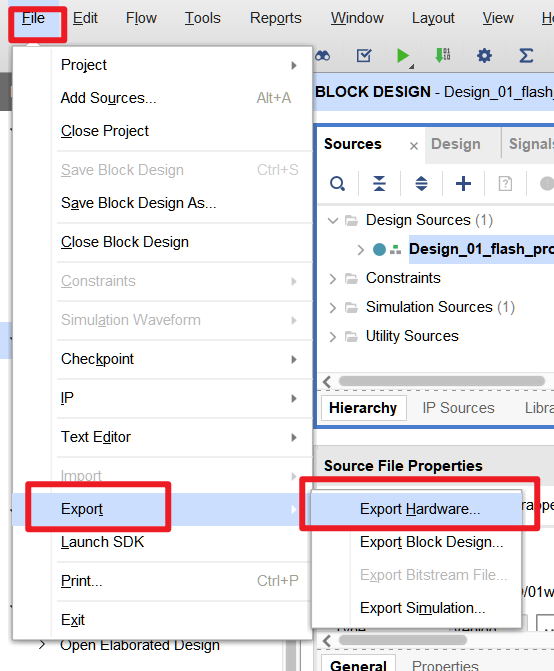

5 导出文件

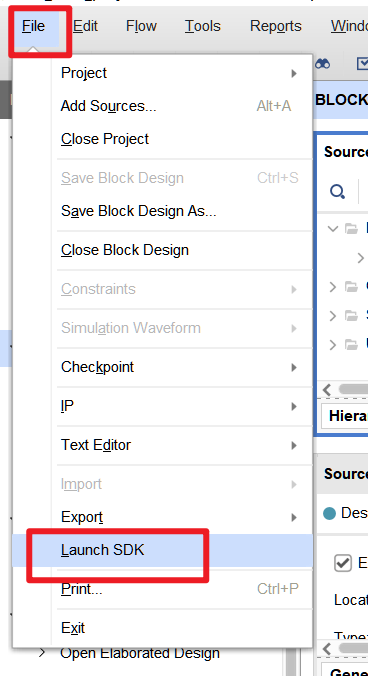

6 打开SDK

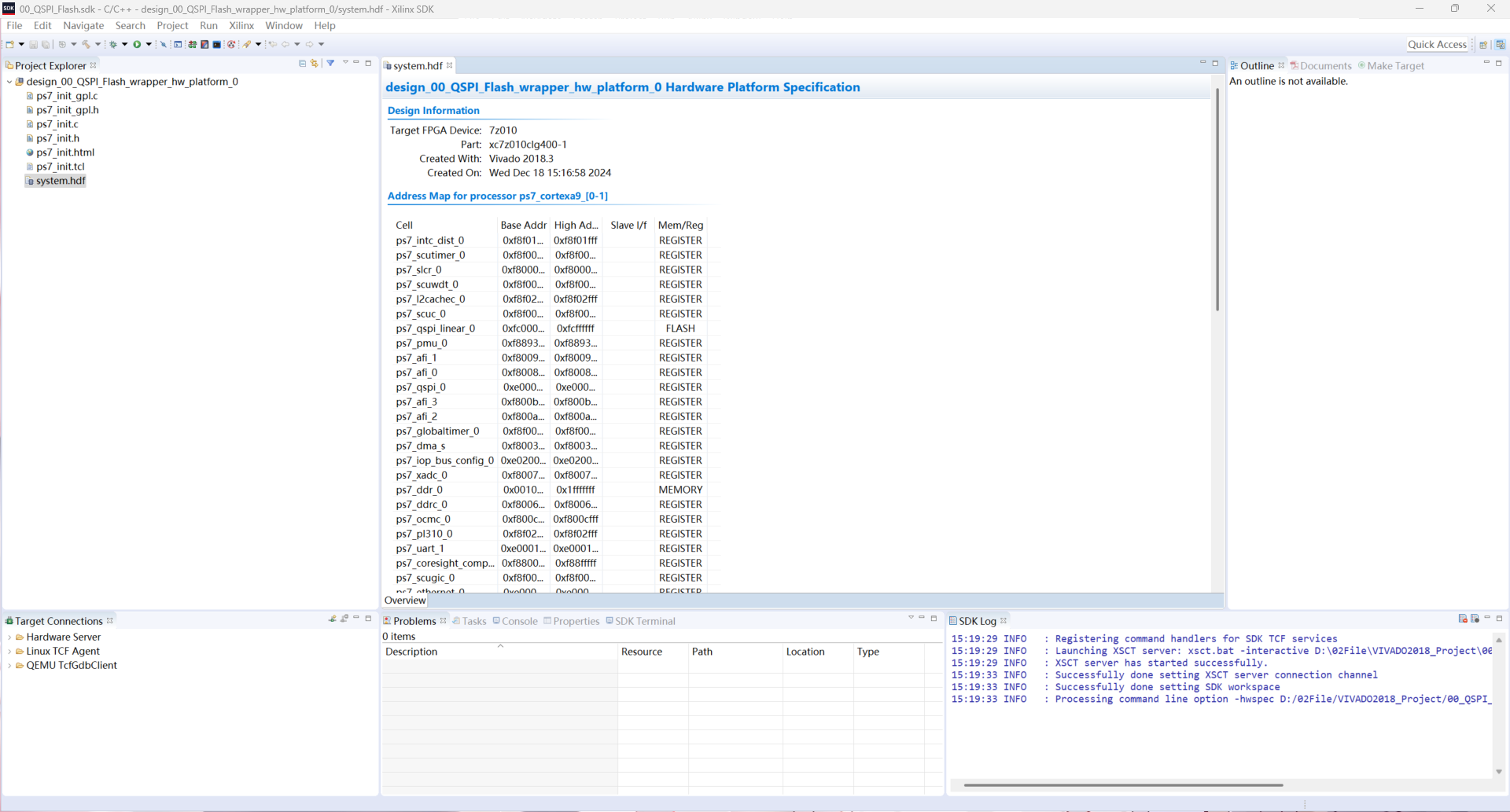

SDK界面如下

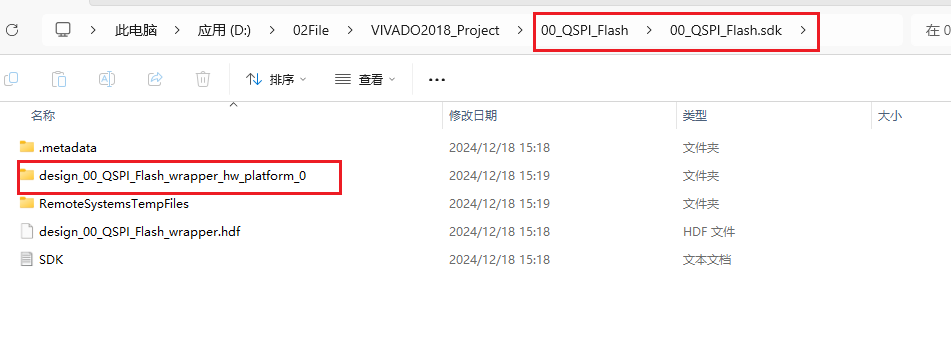

注意这个打开的路径位于VIVADO所创建工程里的....sdk文件,如下所示,后期也可以通过SDK直接找到这个路径打开

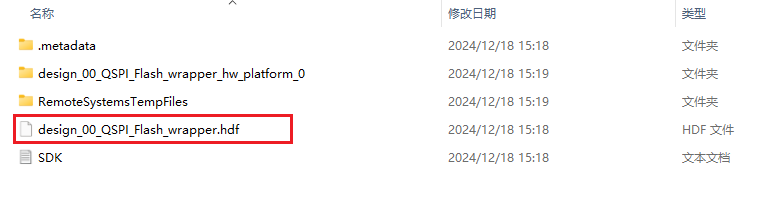

且在这个路径下面便有后续需要使用的.hdf(硬件描述文件)文件

且这个design_00_QSPI_Flash_wrapper.hdf和SDK界面里看到的system.hdf是一样的

openvela 操作系统专为 AIoT 领域量身定制,以轻量化、标准兼容、安全性和高度可扩展性为核心特点。openvela 以其卓越的技术优势,已成为众多物联网设备和 AI 硬件的技术首选,涵盖了智能手表、运动手环、智能音箱、耳机、智能家居设备以及机器人等多个领域。

更多推荐

已为社区贡献14条内容

已为社区贡献14条内容

所有评论(0)