高速接口系列——DP和eDP

维度嵌入式 DisplayPort (eDP)本质外部显示接口标准内部显示接口标准核心价值通用性、高性能、功能丰富(音频、数据、多流)集成度、功耗优化、成本控制技术侧重长距离驱动能力、连接器可靠性、热插拔板级SI、与面板功能深度集成、低电压节能演进驱动游戏、专业创作、超高分辨率桌面显示移动设备续航、轻薄化设计、高刷新率电竞屏结论:DP和eDP共享同一核心协议,但因应用场景不同而走向分化。DP不断突

序:DP和eDP虽然也属于高速串行接口,但与MIPI系列的设计哲学截然不同。需要重点突出三个维度的对比:首先是应用场景的根本差异——DP/eDP面向的是外部显示设备和内部笔记本面板,而C-PHY/D-PHY专注于移动设备内部互联;其次是电气特性的区别,DP采用差分对而eDP兼容多种模式;最关键的是协议层的不同,DP使用微分组包架构且支持AUX通道,这与MIPI的包处理方式形成鲜明对比。

需要特别强调eDP对面板节能的优化设计,比如PSR功能,这是移动设备厂商非常关注的特性。同时要说明尽管eDP物理层可兼容C-PHY,但协议层仍然保持DisplayPort体系,这种混合架构值得详细解释。

测试方面要侧重DisplayPort特有的链路训练和EQ调整机制,这与MIPI的固定模式测试有很大不同。最后需要给出清晰的选择指南,帮助用户根据设备类型、传输距离和功耗要求做出决策。

测试部分要强调DP/eDP在高频下的特殊要求,比如UHBR模式需要50GHz以上示波器进行眼图分析,这对用户的仪器准备有实际指导意义。最后总结时要明确区分外部显示和内部显示的不同技术选择逻辑,帮助用户建立清晰的应用场景映射。

一、协议演进历史:从替代者到王者

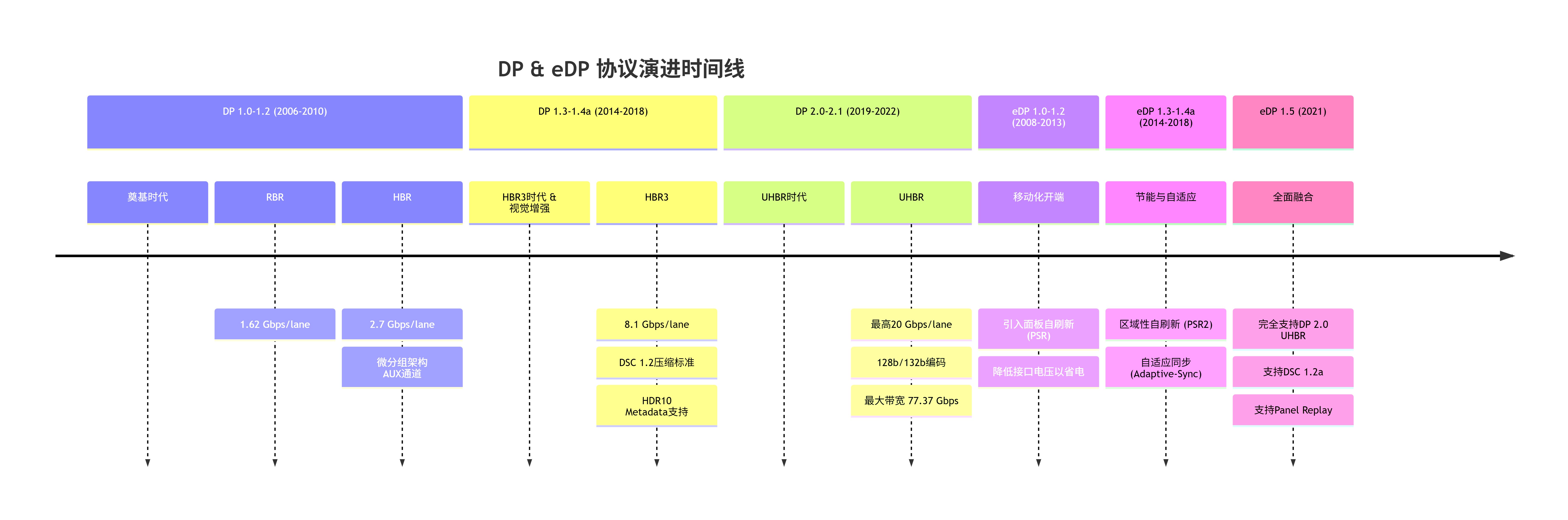

DP和eDP的演进史是一部带宽和功能不断飞跃的历史。其核心发展脉络如下图所示,清晰地展示了速率和关键技术的升级路径:

关键演进技术解读:

-

HBR3 (High Bit Rate 3):在DP 1.3中引入,将单通道速率提升至8.1 Gbps,4通道总带宽达32.4 Gbps,足以支持5K@60Hz等更高规格显示需求。

-

DSC (Display Stream Compression):在DP 1.4中引入的视觉无损压缩技术,是超高分辨率发展的关键助推器。它允许通过压缩视频流来有效降低所需的物理带宽,从而用现有的线缆实现8K@60Hz甚至更高规格的显示。

-

128b/132b编码:DP 2.0弃用了效率为80%的8b/10b编码,转而采用效率高达~97%的128b/132b编码。这是实现超高带宽(UHBR)的核心前提,大幅降低了传输开销。

-

Panel Replay:eDP 1.5引入的革新性功能,可视为PSR的智能化升级。它允许GPU只向面板发送帧间变化的部分(delta),并智能管理面板本地缓存,从而进一步大幅降低数据传输量和系统功耗。

二、技术原理深度解析

1. 微分组包架构:不仅仅是视频流

DP/eDP将视频、音频和控制数据全部打包成微小的数据包进行传输。一个视频流由以下包类型组成:

-

空白间隔数据包:代表水平消隐(HBlank)和垂直消隐(VBlank)时期。

-

视频数据包:包含实际的像素数据。

-

音频数据包:包含时间戳和音频采样数据,可插入到视频流的消隐期内。

这种结构的好处是:

-

内在同步:音频包自带时间戳,可与视频数据在接收端精确同步。

-

强健性:每个包都有CRC校验,接收端可丢弃错误包并请求重传(在双向链路上)。

-

多流传输 (MST):允许将多个独立的视频流(如用于多个显示器)交织在一条物理链路上传输。

2. 链路训练 (Link Training) 详解

链路训练是DP/eDP建立可靠通信的智能握手过程,通过AUX通道进行,分为四个关键阶段:

-

时钟恢复 (Clock Recovery):

-

源端发送TPS1(训练模式1)信号,这是一组固定的、频繁变化的0101模式,便于接收端(SNK)的时钟恢复电路(CDR)快速锁定并同步到源端的符号时钟。

-

-

通道均衡 (Channel Equalization):

-

TPS2:用于比特滑动(Bit Slip) 对齐。由于是多通道并行传输,接收端需要确定每个Lane的字节边界,TPS2帮助接收端对齐各Lane的数据。

-

TPS3/4:用于确定均衡设置。接收端分析信号质量(通过测量眼图宽度/高度),并通过AUX通道反馈给源端,请求其调整预加重(Pre-emphasis) 级别。同时,接收端自身也可能调整均衡器(Equalizer) 的设置。

-

-

参数确认与完成:

-

双方确认最终的链路配置(速率、Lane数、预加重、均衡值)。

-

源端切换到发送视频数据流,接收端开始正常解码。

-

此过程确保了DP/eDP能自动适应不同的线缆长度、质量和PCB损耗,是实现“即插即用”和高可靠性的基石。

三、电气特性与SI要求(以UHBR为例)

DP 2.0 / eDP 1.5的UHBR模式对信号完整性提出了极致的要求。

| 参数 | 要求 (示例, UHBR10/13.5/20) | 测试方法 |

|---|---|---|

| 差分电压幅值 | ~1200mV (峰值) | 高性能示波器,差分探头 |

| 插入损耗 (IL) | 极其严格。e.g., 在 10 GHz 处需优于 -7 dB to -9 dB (取决于速率) | 矢量网络分析仪 (VNA) 测量 SDD21 |

| 回波损耗 (RL) | 在奈奎斯特频率内需优于 -10 dB to -12 dB | VNA测量 SDD11 |

| 模式转换损耗 | 需优于 -20 dB to -25 dB (SCD21) | VNA测量 SCD21 (差分转共模) |

| 总抖动 (TJ) | < 0.15 UI (单位间隔) | 示波器高级抖动分析软件 |

设计注意点:

-

板材选择:实现UHBR必须使用超低损耗板材(如Megtron 6/7/8,IT-968等),普通FR-4材料无法满足要求。

-

布线规范:必须严格控制阻抗(100Ω ±5%),要求差分对内等长(< 5 mil),通道间等长(< 100 ps)。

-

连接器与线缆:DP线缆内的主动式芯片(Redriver或Retimer)几乎是UHBR标准下的必需品。

四、测试与验收:超越眼图

-

物理层测试 (PTT):

-

使用高性能示波器和协议感知软件进行。软件能自动识别并锁定各种训练模式(TPS1-TPS4)和正常数据期,分别进行眼图、抖动和电压参数测量。

-

接收机容限测试 (Rx Margin Test):使用BERT或具备压力输出功能的示波器,向被测接收机注入预加重、抖动、噪声等压力,逐步劣化信号,直到其出现误码(BER > 1e-12),以此衡量其性能裕量。

-

-

协议与功能测试:

-

使用协议分析仪拦截和解析AUX通道通信,验证链路训练流程、EDID读取、MST分配等是否正确。

-

测试eDP专属功能:如触发PSR/PSR2状态切换,验证其功耗确实降低;验证Adaptive-Sync功能是否有效消除撕裂。

-

-

一致性认证:

-

最终产品需要通过VESA授权的认证实验室(ATC)的合规性测试,确保与标准完全兼容,方可使用DP或eDP Logo。

-

总结:技术选型视角

| 维度 | DisplayPort (DP) | 嵌入式 DisplayPort (eDP) |

|---|---|---|

| 本质 | 外部显示接口标准 | 内部显示接口标准 |

| 核心价值 | 通用性、高性能、功能丰富 (音频、数据、多流) | 集成度、功耗优化、成本控制 |

| 技术侧重 | 长距离驱动能力、连接器可靠性、热插拔 | 板级SI、与面板功能深度集成、低电压节能 |

| 演进驱动 | 游戏、专业创作、超高分辨率桌面显示 | 移动设备续航、轻薄化设计、高刷新率电竞屏 |

结论:DP和eDP共享同一核心协议,但因应用场景不同而走向分化。DP不断突破带宽极限,连接外部世界;eDP则深度融合面板技术,专注于极致能效和内部优化。理解其演进历史和底层原理,对于设计和调试现代显示系统至关重要。

openvela 操作系统专为 AIoT 领域量身定制,以轻量化、标准兼容、安全性和高度可扩展性为核心特点。openvela 以其卓越的技术优势,已成为众多物联网设备和 AI 硬件的技术首选,涵盖了智能手表、运动手环、智能音箱、耳机、智能家居设备以及机器人等多个领域。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)