瑞萨RA6T2单片机IIC驱动EEPROM读写实战项目

在嵌入式系统开发中,IIC(Inter-Integrated Circuit)总线因其简洁的双线结构和广泛的应用支持,成为连接低速外设如EEPROM、传感器等器件的重要通信接口。瑞萨RA6T2作为一款面向工业与电机控制领域的高性能Arm® Cortex®-M33内核微控制器,集成了多个增强型IIC模块,具备高可靠性、灵活配置和强大的中断处理能力。其IIC外设通过专用硬件逻辑实现起始/停止信号生成、

简介:本文介绍基于瑞萨RA6T2微控制器实现IIC通信协议驱动EEPROM进行数据读写的完整方案。通过配置RA6T2的IIC模块,结合嵌入式C语言编程,实现对EEPROM的字节写入、随机读取和页写操作,确保数据存储的可靠性与稳定性。项目包含硬件连接设计、IIC时序配置、软件驱动编写及调试方法,适用于工业控制、智能仪表等需要非易失性存储的应用场景。代码经过实测可直接集成到实际工程中,具备良好的可移植性和扩展性。

1. 瑞萨RA6T2微控制器IIC模块概述

在嵌入式系统开发中,IIC(Inter-Integrated Circuit)总线因其简洁的双线结构和广泛的应用支持,成为连接低速外设如EEPROM、传感器等器件的重要通信接口。瑞萨RA6T2作为一款面向工业与电机控制领域的高性能Arm® Cortex®-M33内核微控制器,集成了多个增强型IIC模块,具备高可靠性、灵活配置和强大的中断处理能力。其IIC外设通过专用硬件逻辑实现起始/停止信号生成、地址匹配、ACK/NACK响应及CRC校验等功能,显著降低CPU负担。模块支持主/从双模式运行,内置1字节数据缓冲器与状态机控制逻辑,可精确管理总线时序与仲裁过程,在标准模式(100 kbps)和快速模式(400 kbps)下均能保持稳定通信。

2. EEPROM通信协议与IIC时序配置

在嵌入式系统中,IIC(Inter-Integrated Circuit)总线作为连接微控制器与外部低速外设的核心通信接口之一,其稳定性和精确性直接影响到整个系统的可靠性。尤其在涉及非易失性存储器如EEPROM的读写操作时,必须严格遵循其通信协议规范,并对IIC总线的物理层时序参数进行精准配置。本章将深入探讨EEPROM芯片的通信机制,解析其地址结构、指令帧格式和内部寻址方式;同时结合瑞萨RA6T2微控制器的硬件特性,详细说明如何通过寄存器设置实现符合标准或快速模式要求的IIC通信时序,并借助逻辑分析工具验证实际波形表现。

2.1 EEPROM芯片通信协议解析

EEPROM(Electrically Erasable Programmable Read-Only Memory)作为一种可重复擦写的非易失性存储器件,在工业控制、传感器校准数据保存等场景中广泛应用。其与主控MCU之间的通信通常采用IIC协议,具有接线简洁、协议清晰、兼容性强等优点。理解EEPROM的通信协议是实现可靠读写的前提,核心包括设备地址编码、命令帧结构以及存储空间的寻址机制。

2.1.1 器件地址格式与读写位定义

大多数IIC EEPROM芯片使用7位从机地址,其中部分位由硬件引脚决定,其余为固定前缀。以常见的AT24C系列为例,其地址结构如下表所示:

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| 1 | 0 | 1 | 0 | A2 | A1 | A0 | R/W |

- 高4位 (1010):为制造商预定义的设备类型标识。

- A2/A1/A0 :由外部引脚电平决定,允许同一总线上挂载最多8个相同型号的EEPROM。

- R/W位 :第0位表示操作方向,

0表示写操作,1表示读操作。

例如,若A2=0, A1=1, A0=0,则该设备的7位地址为 1010_010 = 0x52 。发送写命令时,主机会发出 0x52 << 1 | 0 = 0x52 ;读取时则为 0x52 << 1 | 1 = 0x53 。

此地址机制支持多设备共存,但也要求开发者在初始化阶段准确配置目标地址,避免地址冲突导致通信失败。

#define EEPROM_DEVICE_ADDR_BASE 0x50 // AT24Cxx基础地址

#define EEPROM_A2_PIN_LEVEL 0

#define EEPROM_A1_PIN_LEVEL 1

#define EEPROM_A0_PIN_LEVEL 0

uint8_t eeprom_slave_addr = (EEPROM_DEVICE_ADDR_BASE |

((EEPROM_A2_PIN_LEVEL & 0x01) << 2) |

((EEPROM_A1_PIN_LEVEL & 0x01) << 1) |

(EEPROM_A0_PIN_LEVEL & 0x01)) << 1;

代码逻辑逐行解读:

- 第1~4行:定义基础地址及各地址引脚电平状态;

- 第6行:将基础地址

0x50与A2/A1/A0拼接形成完整7位地址;- 左移1位是为了留出最低位用于R/W控制,最终得到一个8位从机地址模板;

- 实际通信中需根据读写需求动态设置最后一位。

这种灵活的地址构造方式使得系统具备良好的扩展能力,尤其适用于需要多个独立存储区域的应用场景。

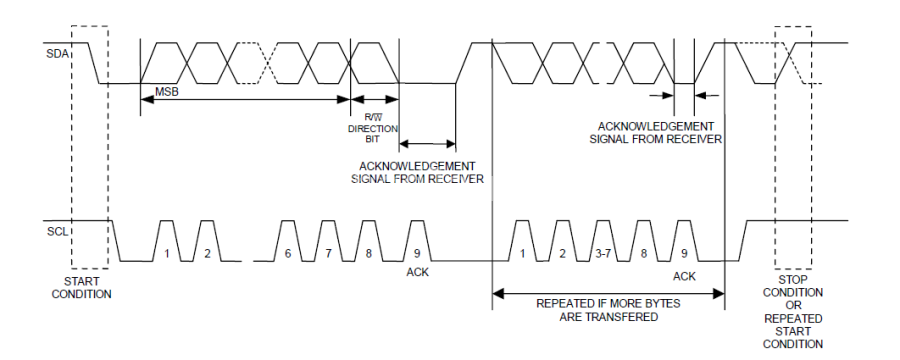

2.1.2 指令帧结构与时序要求

IIC EEPROM的操作遵循严格的帧结构顺序。一次完整的“字节写”过程包含以下步骤:

1. 主机发起 START 条件;

2. 发送 设备地址 + 写位(W=0) ;

3. 接收从机ACK;

4. 发送 内存地址(Memory Address) ——指定写入位置;

5. 接收ACK;

6. 发送 数据字节 ;

7. 接收ACK;

8. 发送 STOP 条件。

对应的读操作更为复杂,通常分为两个阶段:先执行一次“伪写”以定位地址,再重启总线进入读模式。

以下是典型IIC读写流程的状态转换图(使用Mermaid绘制):

stateDiagram-v2

[*] --> IDLE

IDLE --> START: Master sends START

START --> ADDR_WRITE: Send Slave Addr + W=0

ADDR_WRITE --> MEM_ADDR: ACK received

MEM_ADDR --> DATA_WRITE: Send Memory Address

DATA_WRITE --> STOP_WRITE: Send Data & STOP

STOP_WRITE --> RESTART: After delay

RESTART --> START_READ: Send START again

START_READ --> ADDR_READ: Send Slave Addr + R=1

ADDR_READ --> READ_DATA: ACK received

READ_DATA --> RECEIVE_BYTE: Slave sends data

RECEIVE_BYTE --> NACK_LAST: Last byte → NACK

NACK_LAST --> STOP_READ: Send STOP

流程图说明:

- 图中展示了从写地址到读取数据的完整交互流程;

- “RESTART”表示不释放总线的情况下重新开始通信,提高效率并防止其他主机抢占;

- 最后一个字节接收后应返回 NACK ,通知从机停止发送;

- 若未正确处理NACK/ACK,可能导致数据错乱或总线锁定。

这些协议细节决定了驱动程序的设计架构,尤其是在中断或DMA模式下,必须确保每个阶段的时序衔接无误。

2.1.3 内部存储地址寻址机制

EEPROM内部采用线性地址空间管理,地址宽度取决于容量。例如:

- AT24C02(2 Kbit = 256 Bytes):8位地址(0x00 ~ 0xFF)

- AT24C08(8 Kbit = 1024 Bytes):10位地址,高2位来自设备地址A2/A1,低8位来自数据帧

对于超过256字节的EEPROM(如AT24C512),需使用双字节地址字段。此时,在发送设备地址+写命令后,主机需连续发送两个字节的高位地址和低位地址,然后再发送数据。

// 示例:向AT24C512写入数据(双字节地址)

uint8_t addr_high = (target_address >> 8) & 0xFF; // 高8位

uint8_t addr_low = target_address & 0xFF; // 低8位

uint8_t data_byte = 0xAB;

i2c_start();

i2c_write(eeprom_write_addr); // 0xA0

i2c_write(addr_high); // 高地址字节

i2c_write(addr_low); // 低地址字节

i2c_write(data_byte); // 数据字节

i2c_stop();

参数说明与逻辑分析:

target_address范围可达 0~65535(对应512Kbit);- 地址分两次发送,符合IIC协议的数据流格式;

- 所有中间步骤均需检查ACK响应,否则应终止操作并报错;

- 此类大容量EEPROM常用于日志记录、固件备份等大数据量场景。

掌握不同型号EEPROM的寻址规则,有助于构建通用化驱动框架,提升代码复用率。

2.2 IIC总线时序参数设定

IIC总线的电气与时序特性直接决定了通信的稳定性。尽管协议简单,但在高速或长距离传输中,信号完整性容易受到PCB走线、上拉电阻值、电源噪声等因素影响。因此,合理设定时钟频率、上升/下降时间及关键时间参数至关重要。

2.2.1 标准模式与快速模式的时钟频率配置

IIC支持多种速率模式:

- 标准模式(Standard Mode) :最高 100 kbps

- 快速模式(Fast Mode) :最高 400 kbps

- 高速模式(High-speed Mode) :可达 3.4 Mbps(RA6T2暂不支持)

瑞萨RA6T2的SCI/IIC模块可通过配置波特率寄存器(BRL/BRH)生成所需的SCL频率。假设系统主频为 PCLK = 120 MHz ,要实现400 kbps的快速模式,需计算合适的分频系数。

公式如下:

f_{SCL} = \frac{PCLK}{(BRH + 1) \times (Prescaler)}

其中,Prescaler 可选值为1、2、4、8等,由SIMR3寄存器控制。

举例:若选择 Prescaler = 2,期望 f_SCL = 400 kHz,

(BRH + 1) = \frac{120\,MHz}{400\,kHz \times 2} = \frac{120\,000\,000}{800\,000} = 150 → BRH = 149

对应地,BRL也需同步设置(通常等于BRH),以保持高低电平对称。

| 模式 | PCLK (MHz) | Prescaler | BRH Value | Achieved SCL (kHz) |

|---|---|---|---|---|

| Standard | 120 | 4 | 299 | 100.0 |

| Fast | 120 | 2 | 149 | 400.0 |

| Fast+ | 120 | 2 | 99 | 600.0 (超限,不推荐) |

注:超出器件规格可能导致通信不稳定。

该表格可用于初始化阶段自动匹配目标速率。

2.2.2 上升/下降时间对信号完整性的影响

SCL和SDA信号为开漏输出,依赖外部上拉电阻拉高。RC时间常数直接影响边沿陡峭程度。若上升时间过长,可能违反IIC协议中对T_R(rise time)的要求。

根据Philips IIC规范:

- 标准模式:最大 T_R = 1000 ns(300 pF负载)

- 快速模式:最大 T_R = 300 ns(100 pF负载)

假设总线电容 C_bus ≈ 100 pF,选用 R_pullup = 2.2 kΩ,则:

τ = R × C = 2200 × 100e-12 = 220\,ns

T_R ≈ 2.2τ ≈ 484\,ns > 300\,ns → 不满足快速模式要求!

解决方案:

- 减小上拉电阻至1.5 kΩ(代价:静态功耗增加);

- 使用主动上拉电路或缓冲器;

- 缩短PCB走线长度以降低分布电容。

设计建议:优先选用1.8kΩ~2.2kΩ上拉电阻,并在原型阶段用示波器实测上升时间。

2.2.3 T HIGH、T LOW 等关键时序参数计算

除了SCL频率,还需确保各项时序参数符合规范。主要参数包括:

| 参数 | 描述 | 快速模式最小值 | 快速模式最大值 |

|---|---|---|---|

| T_HIGH | SCL高电平持续时间 | 0.6 μs | ∞ |

| T_LOW | SCL低电平持续时间 | 1.3 μs | ∞ |

| T_SU:STA | Repeated START建立时间 | 0.6 μs | – |

| T_HD:DAT | 数据保持时间 | 0 μs | 0.9 μs |

| T_V | 数据有效时间 | – | 3.45 μs |

RA6T2通过硬件自动控制大部分时序,但仍需确认其生成的波形是否合规。例如,当BRH=149时:

- PCLK周期 = 8.33 ns(120 MHz)

- 每个位时间 = (BRH+1) × Prescaler = 150 × 2 = 300 cycles = 2.5 μs

- 半周期约为1.25 μs → T_HIGH ≈ 1.25 μs (>0.6 μs),T_LOW ≈ 1.25 μs (<1.3 μs?)

发现潜在问题:T_LOW略低于规范下限!

解决方法:

- 调整Prescaler为3,BRH=99 → 总周期 = 100×3=300 → 更均衡;

- 或启用“Clock Stretching”功能,允许从机延长T_LOW。

因此,在高可靠性应用中,应结合实测波形优化寄存器配置。

2.3 RA6T2 IIC模块寄存器配置实践

RA6T2的SCI/IIC模块提供丰富的寄存器接口,用于精细控制通信行为。正确配置这些寄存器是实现稳定IIC通信的基础。

2.3.1 波特率发生器(BRL/BRH)设置方法

SCIx_BRR寄存器被复用为IIC模式下的波特率控制。在异步模式下它是单一寄存器,但在IIC同步模式中,需配合SIMR/SIMR3共同作用。

关键寄存器:

- SCIx.BRL / SCIx.BRH :分别设置SCL高/低电平周期计数值;

- SCIx.SIMR3 :设置预分频因子(CKPH, CKPL, STBM);

- SCIx.SCR :使能发送/接收中断与操作模式。

配置流程如下:

// 设置IIC波特率为400kHz,PCLK=120MHz

void configure_i2c_baudrate(void) {

uint8_t brh = 149;

uint8_t brl = 149;

SYSTEM.PRCR.WORD = 0xA502; // 解锁寄存器写保护

SCI2.SCR.BIT.TE = 0; // 关闭发送使能

SCI2.SCR.BIT.RE = 0; // 关闭接收使能

SCI2.SIMR3.BIT.CKPH = 1; // CPOL=1: SCL空闲高

SCI2.SIMR3.BIT.CKPL = 1; // CPHA=1: 数据采样于上升沿?

SCI2.SIMR3.BIT.STBM = 0; // 主模式

SCI2.SSMR.BIT.SCMOD = 2; // IIC主模式

SCI2.BRL = brl;

SCI2.BRH = brh;

SCI2.SCR.BIT.TE = 1;

SCI2.SCR.BIT.RE = 1;

}

参数说明:

CKPH=1表示SCL空闲为高电平(标准IIC);STBM=0设为主机模式;SCMOD=2启用IIC主控模式;- BRL/BRH相等以保证方波输出;

- 必须在禁用TE/RE状态下修改波特率。

该函数应在初始化IIC外设前调用,确保时钟生成准确。

2.3.2 模式控制寄存器(SIMR/SIMR3)配置流程

SCI模块通过多个寄存器组合切换工作模式。关键位说明如下:

| 寄存器 | 位域 | 功能 |

|---|---|---|

| SIMR1.SMR | MMD[1:0] | 模式选择:00=UART, 01=Simple IIC |

| SIMR3 | CKPH, CKPL | 极性和相位控制 |

| SSMR | SCMOS | 是否启用起始/停止条件生成 |

典型配置序列:

SCI2.SIMR1.BIT.MMD = 1; // Simple IIC mode

SCI2.SIMR3.BIT.CKPH = 1; // Clock idle high

SCI2.SIMR3.BIT.CKPL = 1; // Data change on falling edge

SCI2.SSMR.BIT.SCMOS = 1; // Enable START/STOP generation

逻辑分析:

- MMD=1激活IIC协议引擎;

- CKPH/CKPL共同决定SPI-like时序极性,需匹配EEPROM要求;

- SCMOS=1允许硬件自动生成起始/停止信号,减轻CPU负担。

错误配置可能导致无法产生START条件或ACK检测异常。

2.3.3 启用ACK/NACK自动响应机制

在读取最后一个字节时,主机应发送NACK以结束传输。RA6T2支持通过 RXI 中断结合 SIR 寄存器手动控制ACK输出,也可利用自动模式简化流程。

启用自动ACK/NACK:

SCI2.SIMR2.BIT.RXINV = 0; // Normal receive

SCI2.SIMR2.BIT.ACKBR = 0; // 1-bit data per transfer

SCI2.SIMR2.BIT.ACKBT = 0; // 0=NACK after last read

ACKBT=0:最后一次读取后自动发送NACK;ACKBT=1:始终发送ACK;

此外,在接收中断服务程序中可动态判断是否为最后一字节:

void sci2_rxi_isr(void) {

static int byte_count = 0;

if (byte_count == expected_bytes - 1) {

SCI2.SIR.BIT.ACKCT = 1; // Next byte will be NACKed

}

buffer[byte_count++] = SCI2.RDR;

}

优势:

- 自动化程度高,减少中断延迟风险;

- 避免因软件延迟导致NACK发送过晚;

- 提升多字节读取的可靠性。

2.4 实际波形验证与逻辑分析仪调试技巧

即使软件配置正确,仍可能出现通信失败。使用示波器或逻辑分析仪捕获真实信号是诊断问题的关键手段。

2.4.1 使用示波器捕获起始/停止条件

IIC的起始(START)和停止(STOP)条件是识别通信开始与结束的重要标志。

- START :SDA从高→低,而SCL保持高;

- STOP :SDA从低→高,SCL保持高。

操作步骤:

1. 将示波器通道1接SCL,通道2接SDA;

2. 触发方式设为“边沿触发”,通道2下降沿;

3. 执行一次IIC写操作;

4. 观察是否出现标准START波形。

常见问题:

- SDA无变化 → GPIO未正确配置为开漏;

- SCL未变高 → 时钟卡死,可能死锁;

- START/STOP缺失 → 软件未调用start()函数。

2.4.2 分析地址帧与数据帧间的延迟间隙

某些EEPROM在接收到地址后需要短暂准备时间(t_AA)。若主设备连续发送过快,可能导致响应失败。

使用逻辑分析仪可查看完整数据流:

Master: [START] [0xA0] [0x05] [0xAB] [STOP]

Slave: ACK ACK ACK

若第二或第三个ACK丢失,可能是:

- 地址错误;

- EEPROM忙于内部写入;

- 上拉不足导致ACK电平未拉低。

建议添加适当延时或实现ACK轮询机制。

2.4.3 判断总线冲突与异常释放问题

当多个主机同时尝试通信时,可能发生总线竞争。IIC通过SDA仲裁机制解决冲突:任何节点输出高但检测到低时即退出。

调试要点:

- 监测SCL是否被意外拉低;

- 检查STOP后总线是否真正释放(SCL & SDA均为高);

- 若某次通信后总线持续为低,说明某个设备“锁死”了总线。

解决方案:

- 添加看门狗定时器强制复位IIC模块;

- 在初始化时发送9个时钟脉冲帮助从机恢复;

- 使用GPIO模拟方式重置总线。

// 强制释放总线(9 clock pulses)

void i2c_recover_bus(void) {

for (int i = 0; i < 9; i++) {

gpio_set(PIN_SCL, 1);

delay_us(5);

gpio_set(PIN_SDA, 1);

delay_us(5);

gpio_set(PIN_SCL, 0);

delay_us(5);

}

}

此函数可在检测到总线挂起时调用,帮助恢复正常通信。

3. IIC硬件初始化与GPIO引脚配置

在嵌入式系统中,IIC(Inter-Integrated Circuit)总线的稳定运行依赖于底层硬件的正确配置。瑞萨RA6T2微控制器虽然集成了功能强大的IIC外设模块,但若未能合理规划引脚复用、未正确初始化GPIO及外设寄存器,则即使上层协议实现无误,通信仍可能失败。因此,IIC硬件初始化不仅是驱动开发的第一步,更是决定整个通信链路可靠性的基石。本章将围绕RA6T2平台展开从物理引脚到软件抽象层的完整初始化流程,涵盖引脚功能选择、电气特性设计、FSP库调用方式以及中断机制集成等关键环节。

3.1 RA6T2引脚复用功能规划

瑞萨RA6T2基于Arm® Cortex®-M33内核构建,具备丰富的外设资源和灵活的引脚复用机制。其IIC模块通常通过专用引脚SCL(串行时钟线)和SDA(串行数据线)与其他设备通信。这些引脚并非固定绑定某一个端口,而是可通过“复用功能选择”机制映射至多个可用GPIO端子。这种灵活性提高了PCB布局自由度,但也要求开发者精确配置相关寄存器以确保信号路径正确建立。

3.1.1 IIC专用引脚(SCL/SDA)的Port寄存器设置

RA6T2采用一组标准化的端口控制寄存器(如PFR、PMR、PODR、PIDR等)来管理每个GPIO的功能状态。以使用P407作为SDA、P406作为SCL为例,在启用IIC0通道时,必须先禁用其通用输出功能,并将其切换为“替代功能模式”。这一过程涉及以下核心寄存器:

| 寄存器 | 功能说明 |

|---|---|

| PFRn | 引脚功能选择寄存器,用于设定是否启用复用功能 |

| PMRn | 模式控制寄存器,决定引脚是普通IO还是外设功能 |

| ODRn | 输出驱动能力调节寄存器(如开漏/推挽) |

| PCRn | 上拉电阻使能寄存器 |

// 示例代码:配置P406(SCL)和P407(SDA)为IIC0复用功能

R_PORT4->PFR_b.PFR6 = 0; // 清除原功能位

R_PORT4->PFR_b.PFR7 = 0;

R_PORT4->PMR_b.PMR6 = 1; // 启用复用功能

R_PORT4->PMR_b.PMR7 = 1;

R_PORT4->PFR_b.PFR6 = 1; // 设置为AF1(假设IIC0对应AF1)

R_PORT4->PFR_b.PFR7 = 1;

逐行逻辑分析:

R_PORT4->PFR_b.PFR6 = 0;:首先清除当前引脚的功能选择位,防止残留配置干扰。R_PORT4->PMR_b.PMR6 = 1;:激活复用模式,允许该引脚接受外设控制。R_PORT4->PFR_b.PFR6 = 1;:指定该引脚连接至第一个替代功能(AF1),此处需查阅数据手册确认IIC0对应的AF编号。

此三步构成了典型的“清零→设模式→选功能”的安全配置序列,避免因并发写操作导致不可预测行为。

3.1.2 复用模式选择(AF Function Setting)

RA6T2支持最多8种替代功能(AF0 ~ AF7),每组引脚的具体映射关系记录在《RA6T2 User’s Manual: Hardware》的“Pin Functions Table”中。例如,IIC0_SDA可分配给P407、P501等多个引脚,但同一时刻只能启用其中一个。选择合适引脚应综合考虑PCB走线长度、噪声隔离以及与其他外设的冲突情况。

下表展示了部分IIC通道与典型引脚的映射关系:

| IIC Channel | SCL Pin(s) | SDA Pin(s) | 默认AF编号 |

|---|---|---|---|

| IIC0 | P406, P500 | P407, P501 | AF1 |

| IIC1 | P304, P902 | P305, P903 | AF2 |

| IIC2 | P114, P120 | P115, P121 | AF3 |

⚠️ 注意:不同封装型号可能略有差异,请以具体芯片型号为准。

在实际工程中,推荐使用瑞萨e² studio工具链中的Configuration Wizard自动完成AF配置,生成符合FSP规范的初始化代码。然而理解底层寄存器操作对于调试引脚锁定或功能错位问题至关重要。

3.1.3 开漏输出与上拉电阻设计规范

IIC总线采用开漏(Open-Drain)输出结构,这意味着SCL和SDA引脚只能主动拉低电平,无法直接驱动高电平。因此,外部必须连接上拉电阻(Pull-up Resistor)至VDD(通常为3.3V或5V),利用电阻实现电平恢复。

flowchart LR

MCU[MCU SDA/SCL] -->|OD Output| BUS[IIC Bus]

BUS --> R1[Rpull-up 4.7kΩ]

R1 --> VDD[VDD 3.3V]

DEVICE[EEPROM or Sensor] -->|OD Output| BUS

如上图所示,总线上所有设备均以开漏形式接入,任何一方均可发起拉低动作,从而实现“线与”逻辑,这是实现仲裁和同步的基础。

根据IIC标准模式(100 kbps)和快速模式(400 kbps)的要求,上拉电阻值需满足以下条件:

- 过小电阻 :导致上升时间过短,增加功耗并可能引起电磁干扰;

- 过大电阻 :上升沿缓慢,违反T R (rise time)参数限制,造成采样错误。

参考公式:

R_{pull-up} \geq \frac{V_{DD} - V_{OL}}{I_{OL}},\quad

t_r \leq 0.3 \times T_{clock}

结合RA6T2电气特性(最大灌电流8mA,典型VOL=0.4V),选取4.7kΩ较为稳妥。对于长距离布线或高容性负载(>400pF),建议降低至2.2kΩ以加快上升速度。

此外,RA6T2部分端口内置可编程上拉电阻(通过PCR寄存器控制),但在IIC应用中不推荐使用内部上拉,因其阻值较大(约100kΩ~1MΩ),不足以驱动总线快速充电。务必外接精密贴片电阻。

3.2 基于FSP库的IIC驱动初始化流程

瑞萨Flexible Software Package(FSP)提供了高度抽象的IIC主/从模式驱动接口,极大简化了外设初始化工作。相比直接操作寄存器,使用FSP不仅提升开发效率,还能保证跨平台兼容性和中断处理一致性。

3.2.1 创建IIC控制块与配置结构体

FSP采用面向对象的设计思想,每个外设实例由“控制块(Control Block)”和“配置结构体(Config Structure)”共同构成。以下是初始化IIC0为主机模式的关键结构定义:

static iic_master_ctrl_t g_iic0_ctrl;

static iic_master_cfg_t g_iic0_cfg = {

.slave = 0x50, // 目标EEPROM地址

.rate = IIC_MASTER_RATE_STANDARD,// 100kbps

.spec_version = IIC_MASTER_BUS_SPEC_VERSION_2,

.timeout = {

.start_bit = 100,

.stop_bit = 100,

.address = 100,

.transfer = 100

},

.p_extend = NULL,

.irq = IIC_IRQ_TEI0, // 传输结束中断

.ipl = 4 // 中断优先级

};

参数说明:

- .slave :目标从机7位地址左移一位后填入,最低位由读写操作动态决定;

- .rate :支持 IIC_MASTER_RATE_STANDARD (100kbps)、 FAST (400kbps)等;

- .timeout :各阶段超时计数(单位为系统滴答),防止死锁;

- .irq 和 .ipl :关联中断源与优先级,实现异步通知。

该结构体在编译期静态初始化,确保内容位于已知内存区域,便于运行时访问。

3.2.2 配置主模式、时钟速率及超时参数

在调用 R_IIC_MASTER_Open() 之前,还需指定使用的IIC基地址和引脚配置。FSP通过 iic_master_instance_t 类型封装实例信息:

const iic_master_instance_t g_iic0 = {

.p_api = &g_iic_master_on_iic,

.p_ctrl = &g_iic0_ctrl,

.p_cfg = &g_iic0_cfg

};

其中 .p_api 指向全局API函数表,包含 open , read , write , close 等标准方法。这种设计实现了多实例共用一套API逻辑,符合POSIX风格驱动模型。

时钟速率的实际分频由波特率发生器(BRL/BRH)自动计算。FSP内部依据系统PCLK频率(如120MHz)和用户设定的 .rate 字段,调用 iic_calculate_baud() 函数生成合适的BRL/BRH值,无需手动查表。

3.2.3 调用R_IIC_MASTER_Open()完成初始化

完成上述准备后,即可执行正式初始化:

fsp_err_t err = R_IIC_MASTER_Open(g_iic0.p_ctrl, g_iic0.p_cfg);

if (err != FSP_SUCCESS) {

// 错误处理:打印日志或进入安全状态

while(1);

}

该函数执行如下操作:

1. 检查参数合法性;

2. 配置IICxSIMR、IICxBRH/L寄存器;

3. 启动模块电源与时钟门控;

4. 注册中断服务程序(ISR);

5. 将模块置于待机状态(等待首次启动)。

成功返回 FSP_SUCCESS 表示IIC硬件已就绪,可进行后续读写操作。

sequenceDiagram

participant App as Application

participant FSP as FSP IIC Driver

participant HW as RA6T2 IIC Module

App->>FSP: R_IIC_MASTER_Open()

FSP->>HW: Enable Clock & Reset Module

FSP->>HW: Set BRL/BRH for Target Rate

FSP->>HW: Configure SIMR for Master Mode

FSP->>App: Return FSP_SUCCESS

此流程体现了硬件抽象层的价值:屏蔽复杂寄存器细节,暴露简洁API接口。

3.3 中断服务程序注册与事件回调机制

为了实现高效的非阻塞通信,IIC传输必须依赖中断驱动机制。RA6T2的IIC模块支持多种中断源,包括发送缓冲空中断(TXI)、接收缓冲满中断(RXI)、传输结束中断(TEI)等,合理利用这些事件可显著降低CPU轮询开销。

3.3.1 绑定IIC传输完成中断ISR

在FSP框架中,中断服务程序(ISR)通过配置结构体中的 .irq 字段自动注册。开发者只需提供回调函数:

void iic_callback(iic_master_callback_args_t *p_args)

{

switch(p_args->event) {

case IIC_MASTER_EVENT_TX_COMPLETE:

g_tx_done = true;

break;

case IIC_MASTER_EVENT_RX_COMPLETE:

g_rx_done = true;

break;

case IIC_MASTER_EVENT_ABORTED:

g_error_flag = p_args->status;

break;

default:

break;

}

}

// 初始化时注入回调

g_iic0_cfg.callback = iic_callback;

当一次 R_IIC_MASTER_Write() 完成后,硬件触发TEI中断,FSP ISR捕获该事件并调用用户注册的 iic_callback 函数,传入包含事件类型和状态码的参数结构体。

3.3.2 处理TXI/RXI/TEI等关键中断源

各中断源的作用如下:

| 中断源 | 触发条件 | 典型用途 |

|---|---|---|

| TXI | 发送缓冲区空 | 连续写入多字节时填充下一数据 |

| RXI | 接收缓冲区满 | 读取刚收到的数据字节 |

| TEI | 整个传输完成 | 标记事务结束,释放信号量 |

例如,在页写操作中,若启用TXI中断,则可在每次发送一字节后立即填充下一笔数据,形成流水线式发送:

void iic_callback(...) {

if (p_args->event == IIC_MASTER_EVENT_TX_DATA_EMPTY) {

if (g_data_index < g_total_bytes) {

R_IIC_MASTER_Write(&g_iic0_ctrl, &g_buffer[g_data_index++], 1, false);

}

}

}

这种方式避免了长时间阻塞主线程,适用于实时性要求高的工业控制系统。

3.3.3 实现非阻塞式数据传输框架

结合FreeRTOS或状态机,可构建完整的异步通信框架:

typedef enum {

IDLE,

WRITING_ADDR,

WRITING_DATA,

READING,

DONE

} iic_state_t;

static iic_state_t g_iic_state;

void iic_callback(...) {

switch(p_args->event) {

case IIC_MASTER_EVENT_TX_COMPLETE:

switch(g_iic_state) {

case WRITING_ADDR:

g_iic_state = WRITING_DATA;

R_IIC_MASTER_Write(...); // 继续写数据

break;

case WRITING_DATA:

g_iic_state = DONE;

xSemaphoreGive(g_iic_sem); // 通知任务完成

break;

}

break;

}

}

该模式下,主任务仅发起请求即刻返回,由中断驱动状态转移,极大提升了系统吞吐能力和响应速度。

3.4 引脚电平测试与硬件连通性验证

即便软件配置无误,若硬件连接存在问题(如虚焊、短路、上拉缺失),IIC总线仍将无法正常工作。因此,在系统上电初期进行引脚电平检测至关重要。

3.4.1 上电后SCL/SDA静态电平检测

理想情况下,空闲状态下SCL和SDA均应被上拉电阻维持在高电平(接近VDD)。可通过简单读取PIDR寄存器验证:

uint8_t scl_level = R_PORT4->PIDR_b.PID6;

uint8_t sda_level = R_PORT4->PIDR_b.PID7;

if (scl_level == 0 || sda_level == 0) {

// 总线被异常拉低,可能存在短路或从机卡死

error_handler(IIC_BUS_STUCK_LOW);

}

若发现任一信号持续为低,应检查:

- 是否存在从设备电源未上电却连接总线;

- PCB是否存在锡桥或ESD损伤;

- 上拉电阻是否焊接正确。

3.4.2 模拟空闲状态下的总线释放行为

在主机未启动IIC模块前,应确保SCL/SDA处于高阻态。可通过临时配置为输入模式模拟释放:

R_PORT4->PMR_b.PMR6 = 0; // 退出复用模式

R_PORT4->PMR_b.PMR7 = 0;

R_PORT4->PMC_b.PMC6 = 1; // 设为输入

R_PORT4->PMC_b.PMC7 = 1;

此时测量引脚电压,若仍不能升至高电平,则表明外部电路存在问题。

3.4.3 排查短路或上拉失效导致的通信失败

常见故障排查表格如下:

| 现象 | 可能原因 | 解决方案 |

|---|---|---|

| SDA始终为低 | 从机损坏或地址冲突 | 断开所有从机逐一排查 |

| SCL波动但无ACK | 时钟频率过高或负载过大 | 降低速率或减小总线电容 |

| 读写超时 | 上拉电阻开路 | 更换为4.7kΩ新电阻 |

| NACK频繁出现 | 地址错误或器件未就绪 | 使用逻辑分析仪抓包比对 |

推荐使用Saleae Logic Pro或DSLogic等USB逻辑分析仪实时观测波形,辅助定位协议层问题。

综上所述,IIC硬件初始化是一个融合软硬件协同设计的过程。只有在引脚配置精准、电气设计合规、驱动初始化严谨的前提下,才能保障后续EEPROM读写操作的顺利开展。

4. EEPROM读写操作的编程实现

在嵌入式系统中,对非易失性存储器如EEPROM的可靠读写是保障数据持久化和配置信息保存的关键环节。瑞萨RA6T2微控制器凭借其增强型IIC模块,能够高效、稳定地与外部串行EEPROM芯片(如AT24C系列)进行通信。本章将深入探讨如何基于RA6T2的硬件IIC外设,结合FSP(Flexible Software Package)框架,完整实现EEPROM的字节写入、随机读取、页写优化以及错误处理机制。通过精细化控制IIC协议流程,确保每次操作符合EEPROM器件的数据手册规范,尤其关注内部写周期等待、地址定位方式、ACK/NACK响应管理等关键细节。

4.1 字节写入(Byte Write)操作实现

4.1.1 发送设备地址+写命令的起始序列

EEPROM的IIC通信始于一个标准的起始条件(START),随后主控器发送设备地址帧。该地址由固定前缀(通常为 1010 )、片选位(A2/A1/A0引脚电平决定)和读写方向位组成。以常见的AT24C64为例,其7位设备地址范围为 0b1010000 至 0b1010111 ,具体取决于硬件连接。当执行写操作时,最低位设置为 0 ,即表示“写模式”。

在RA6T2上使用FSP库时,可通过 g_i2c_master5.p_api->write() 函数发起写请求。底层驱动会自动构造包含起始条件、设备地址及写标志的传输序列,并等待从机应答(ACK)。若SDA线未被拉低,则说明目标设备未响应,可能由于电源异常、地址错误或总线冲突导致。

以下为一次完整的字节写操作中设备地址发送阶段的代码示例:

// 定义EEPROM设备地址(7位格式)

#define EEPROM_DEVICE_ADDR (0x50U) // AT24C64 常见地址

// 写入缓冲区:[内存地址][数据]

uint8_t write_buffer[2] = {0x00, 0xAB};

// 调用FSP IIC Master API 执行写操作

fsp_err_t err = g_i2c_master5.p_api->write(g_i2c_master5.p_ctrl,

write_buffer,

2,

EEPROM_DEVICE_ADDR,

false); // 不产生重复启动

逻辑分析与参数说明:

write_buffer: 包含两个字节,第一个为EEPROM内部存储地址(0x00),第二个为待写入的数据(0xAB)。2: 表示要发送的总字节数,包括地址和数据。EEPROM_DEVICE_ADDR: 7位设备地址,驱动内部会自动左移并补0作为写操作标识。false: 指定本次传输结束后是否生成停止条件。若后续需立即发起读操作,可设为true以保留总线占用(即不发STOP),用于实现“重启”(Repeated START)。

此过程对应的IIC总线时序如下图所示(Mermaid流程图):

sequenceDiagram

participant MCU as RA6T2 (Master)

participant EEPROM as EEPROM (Slave)

MCU->>EEPROM: START

MCU->>EEPROM: SLA_W (0xA0)

EEPROM-->>MCU: ACK

MCU->>EEPROM: Memory Address (0x00)

EEPROM-->>MCU: ACK

MCU->>EEPROM: Data Byte (0xAB)

EEPROM-->>MCU: ACK

MCU->>EEPROM: STOP

该图清晰展示了从起始信号到最终停止的完整字节写入流程。每个ACK均由EEPROM返回,确认其已正确接收每一帧数据。

此外,为验证实际波形是否符合预期,建议配合逻辑分析仪抓取SCL与SDA信号,检查起始/停止条件、地址对齐与时序合规性。特别注意,在快速模式下(400 kbps),上升时间不得超过300ns,否则可能导致误判。

4.1.2 连续发送目标地址与待写数据字节

在完成设备地址发送后,紧接着需传输目标存储地址(Memory Address),再紧随其后的是实际要写入的数据内容。对于支持多字节地址的EEPROM(如AT24C512以上型号),需要连续发送两个地址字节(高位在前),而对于较小容量的器件(≤64Kbit),通常只需一个字节地址即可寻址全部空间。

RA6T2的IIC模块支持连续数据流发送,无需手动插入延时。但在应用层设计中,必须保证 write_buffer 数组结构正确组织。例如,向地址0x1234写入值0xCD的操作应构造如下缓冲区:

uint8_t write_buffer[3];

write_buffer[0] = 0x12; // 高地址字节

write_buffer[1] = 0x34; // 低地址字节

write_buffer[2] = 0xCD; // 数据字节

err = g_i2c_master5.p_api->write(g_i2c_master5.p_ctrl,

write_buffer,

3,

EEPROM_DEVICE_ADDR,

true);

上述调用将一次性发送三字节数据流,期间无中断或重启动。这种“地址+数据”的紧凑格式极大提升了通信效率,避免了多次独立事务带来的开销。

为了更直观理解不同EEPROM型号的地址长度差异,下表列出常用AT24C系列的特性对比:

| 型号 | 容量 (Kbit) | 地址长度 | 设备地址引脚 | 最大页大小 |

|---|---|---|---|---|

| AT24C02 | 2 | 1 byte | A0-A2 | 8 bytes |

| AT24C08 | 8 | 1 byte | A0-A2 | 16 bytes |

| AT24C32 | 32 | 2 bytes | A0-A2 | 32 bytes |

| AT24C64 | 64 | 2 bytes | A0-A2 | 32 bytes |

| AT24C512 | 512 | 2 bytes | A0-A1 | 128 bytes |

注意 :虽然AT24C512容量较大,但仍仅使用2字节地址,最高支持64KB寻址空间。超过此范围需借助芯片选择线或多器件并联。

在软件层面,推荐封装一个通用写函数,根据设备类型动态调整地址长度:

typedef struct {

uint16_t mem_addr;

uint8_t data;

uint8_t addr_bytes; // 1 或 2

} eeprom_write_cmd_t;

void eeprom_byte_write(eeprom_write_cmd_t *cmd) {

uint8_t buf[3];

if (cmd->addr_bytes == 2) {

buf[0] = (cmd->mem_addr >> 8) & 0xFF;

buf[1] = cmd->mem_addr & 0xFF;

buf[2] = cmd->data;

g_i2c_master5.p_api->write(..., buf, 3, ...);

} else {

buf[0] = cmd->mem_addr & 0xFF;

buf[1] = cmd->data;

g_i2c_master5.p_api->write(..., buf, 2, ...);

}

}

此抽象提高了代码复用性和可维护性,适用于多种EEPROM型号共存的应用场景。

4.1.3 等待EEPROM内部写周期完成(ACK Polling)

EEPROM在接收到写指令后,并不会立即响应新的访问请求。其内部需要一段时间(典型值5~10ms)来完成电荷注入与浮栅编程。在此期间,即使主机尝试与其通信,也不会得到有效的ACK响应。因此,必须实施“ACK轮询”(ACK Polling)机制,主动探测设备是否已准备好接受下一次操作。

实现方法如下:持续尝试向目标设备发送一个仅包含设备地址(SLA+W)的写请求,直到获得ACK为止。一旦成功收到ACK,表明写周期结束,可以继续后续操作。

bool eeprom_wait_until_ready(void) {

fsp_err_t err;

int retry = 100; // 最多重试100次,约500ms超时

do {

err = g_i2c_master5.p_api->write(g_i2c_master5.p_ctrl,

NULL,

0,

EEPROM_DEVICE_ADDR,

true); // 不发送数据,仅检测ACK

R_BSP_SoftwareDelay(1, BSP_DELAY_UNITS_MILLISECONDS);

} while ((err != FSP_SUCCESS) && (--retry > 0));

return (err == FSP_SUCCESS);

}

逐行解析:

NULL和0: 表示不发送任何数据,仅发送起始+地址帧。true: 使用重复启动(Repeated START),便于快速重试。R_BSP_SoftwareDelay(1, ...): 每次尝试间隔1ms,防止频繁总线占用。- 循环最多执行100次,覆盖最坏情况下的写周期延迟。

该机制简单而有效,广泛应用于各类IIC EEPROM驱动开发中。值得注意的是,某些高端EEPROM支持“就绪引脚”(RDY/BUSY),可通过GPIO直接查询状态,从而减少总线轮询负担。但在缺乏此类引脚的情况下,ACK Polling仍是标准做法。

4.2 随机读取(Random Read)操作流程

4.2.1 先执行伪写操作定位存储地址

IIC EEPROM的随机读取并非直接发送读命令,而是遵循“先定位后读取”的两步法。第一步称为“伪写”(Dummy Write),即发起一次不携带数据的写操作,仅用于传递目标存储地址。该操作完成后不真正写入数据,但会使EEPROM内部指针指向指定位置。

在RA6T2平台上,这一过程可通过一次短写完成:

uint8_t addr_buf[2] = {0x00, 0x10}; // 要读取的地址:0x0010

fsp_err_t err = g_i2c_master5.p_api->write(g_i2c_master5.p_ctrl,

addr_buf,

2, // 根据设备选择1或2字节

EEPROM_DEVICE_ADDR,

true); // 保持总线活跃(Re-START)

此处关键在于最后一个参数设为 true ,表示不发出STOP信号,以便紧接着发起读操作。这一步完成后,EEPROM已更新内部地址指针。

4.2.2 重启总线并切换至读模式

在伪写之后,主控器需立即发送一个 重复起始条件 (Repeated START),然后发送设备地址并设置读方向位(R/W = 1)。此时,EEPROM将开始在其当前地址处输出数据。

uint8_t read_data;

err = g_i2c_master5.p_api->read(g_i2c_master5.p_ctrl,

&read_data,

1,

EEPROM_DEVICE_ADDR,

false); // 此次完成后释放总线

read() 调用会在内部自动生成Re-START + SLA+R序列,并接收单个字节。整个流程如下表所示:

| 阶段 | SDA 数据流 | 方向 |

|---|---|---|

| 起始 | START | → |

| 发送设备地址 | 1 0 1 0 A2 A1 A0 0 | → |

| 接收ACK | ACK | ← |

| 发送地址高字节 | D7 D6 D5 D4 D3 D2 D1 D0 | → |

| 接收ACK | ACK | ← |

| 发送地址低字节 | D7 D6 D5 D4 D3 D2 D1 D0 | → |

| 接收ACK | ACK | ← |

| 重复起始 | Re-START | → |

| 发送设备地址+读 | 1 0 1 0 A2 A1 A0 1 | → |

| 接收ACK | ACK | ← |

| 接收数据 | D7 D6 D5 D4 D3 D2 D1 D0 | ← |

| 发送NACK | NACK | → |

| 停止 | STOP | → |

4.2.3 接收数据并正确发送最后一个NACK

在IIC协议中,接收方应在最后一个字节接收后主动发送 NACK ,以通知从机停止继续发送数据。这是协议强制要求,否则EEPROM将持续输出下一个地址的内容。

在FSP库中, read() 函数的行为由传入的字节数控制:

- 若读取 n 字节,最后第 n 个字节后自动发送NACK并STOP。

- 若需连续读取多个字节并手动控制NACK时机,可使用异步模式配合中断回调。

示例如下:

// 读取连续4字节,最后一个自动NACK

uint8_t data[4];

g_i2c_master5.p_api->read(ctrl, data, 4, addr, false);

若需实现“流式读取”,可在中断服务程序中动态决定何时终止接收。这种方式更适合大数据块传输或DMA集成场景。

下面展示完整的随机读操作流程图(Mermaid):

graph TD

A[Start] --> B[Send SLA+W]

B --> C{ACK?}

C -- Yes --> D[Send Mem Addr H/L]

C -- No --> Z[Error: Device Not Ready]

D --> E{ACK?}

E -- Yes --> F[Repeated START]

F --> G[Send SLA+R]

G --> H{ACK?}

H -- Yes --> I[Receive Data Bytes]

I --> J[Send NACK on Last Byte]

J --> K[STOP]

K --> L[Operation Complete]

该图体现了状态转移逻辑,有助于构建健壮的状态机驱动模型。

4.3 页写(Page Write)批量数据优化策略

4.3.1 计算EEPROM页面边界与最大写长度

大多数EEPROM采用“页写”机制,允许一次写入多个连续字节(称为一页),但禁止跨页写入。若写操作跨越页边界,超出部分将回卷至页首,造成数据错乱。因此,必须精确计算每页的起始地址和长度。

以AT24C64为例,其页大小为32字节,页边界位于 X*32 处。若当前写地址为0x002A,剩余可用空间仅为6字节(0x002B~0x002F)。因此,最大安全写长度为:

#define PAGE_SIZE 32

uint8_t remaining = PAGE_SIZE - (address % PAGE_SIZE);

编写页写函数时应首先判断是否跨页:

void eeprom_page_write(uint16_t start_addr, uint8_t *data, size_t len) {

size_t offset = start_addr % PAGE_SIZE;

size_t first_chunk = (offset + len > PAGE_SIZE) ?

(PAGE_SIZE - offset) : len;

// 第一块:不超过页尾

uint8_t buffer[34]; // 地址(2)+数据

buffer[0] = (start_addr >> 8) & 0xFF;

buffer[1] = start_addr & 0xFF;

memcpy(buffer + 2, data, first_chunk);

g_i2c_master5.p_api->write(..., buffer, 2 + first_chunk, ..., true);

eeprom_wait_until_ready();

// 若有剩余,拆分第二笔写入

if (first_chunk < len) {

eeprom_page_write(start_addr + first_chunk,

data + first_chunk,

len - first_chunk);

}

}

4.3.2 分块写入避免跨页覆盖风险

跨页写入是常见错误源。通过分块策略可彻底规避该问题。上例中使用递归方式处理剩余数据,也可改为循环迭代提升性能。

此外,建议建立页信息查找表,针对不同型号预定义页大小:

| 型号 | 页大小 | 写周期最大时间 |

|---|---|---|

| AT24C02 | 8 | 5 ms |

| AT24C04 | 16 | 5 ms |

| AT24C16 | 16 | 5 ms |

| AT24C32 | 32 | 5 ms |

| AT24C64 | 32 | 5 ms |

| AT24C512 | 128 | 5 ms |

运行时可根据设备类型加载相应参数,提高通用性。

4.3.3 提升大数据量写入效率的调度算法

对于大量数据写入(如固件日志、校准参数),可引入“批处理+延迟合并”策略:

- 缓冲最近修改的数据;

- 定期统一提交至EEPROM;

- 利用页写最大化吞吐率;

- 结合CRC校验防止中途断电导致损坏。

示例调度结构体:

typedef struct {

uint16_t addr;

uint8_t data[128];

size_t len;

bool dirty;

} eeprom_write_queue_t;

配合定时器中断定期刷新队列,显著降低频繁小写带来的磨损和延迟。

4.4 错误处理与健壮性增强机制

4.4.1 检测NACK响应并判断设备未就绪

NACK出现在以下几种情形:

- 设备地址错误;

- EEPROM正处于写周期;

- 总线被其他主机占用;

- 器件故障或掉电。

FSP API 返回 FSP_ERR_I2C_NACK 时表示收到NACK。应据此触发重试逻辑:

if (err == FSP_ERR_I2C_NACK) {

// 可能正在写入,等待后再试

eeprom_wait_until_ready();

}

4.4.2 超时重试机制与错误状态上报

所有IIC操作应设置合理的超时与重试次数:

int retries = 3;

while (retries--) {

err = i2c_write(...);

if (err == FSP_SUCCESS) break;

R_BSP_SoftwareDelay(10, BSP_DELAY_UNITS_MILLISECONDS);

}

if (err != FSP_SUCCESS) {

log_error("EEPROM write failed after 3 retries");

return -1;

}

4.4.3 添加CRC校验确保数据一致性

为防止数据损坏,可在写入时附加CRC-16校验码:

uint16_t crc = calc_crc16(data, len);

append_to_eeprom(addr, data, len);

append_to_eeprom(addr+len, (uint8_t*)&crc, 2);

读取时重新计算并比对,提升系统可靠性。

综上所述,EEPROM读写不仅是简单的寄存器操作,更是涉及协议细节、时序控制、错误恢复与性能优化的综合性工程任务。合理运用RA6T2的硬件能力与FSP库接口,辅以严谨的设计模式,方可构建出高可用的嵌入式存储子系统。

5. 软件模拟IIC与系统级稳定性优化

5.1 硬件IIC与软件模拟IIC的对比分析

在瑞萨RA6T2的实际应用中,虽然其内置的硬件IIC模块具备高效率、低CPU占用和自动协议处理等优势,但在某些特殊场景下仍需采用 软件模拟IIC(Bit-Banging) 。例如:

- 所有硬件IIC通道已被占用;

- 需要非标准时序(如极慢速通信以兼容老旧EEPROM);

- 引脚位置受限,无法使用专用IIC引脚;

- 多设备共用总线且存在电平冲突风险。

| 对比维度 | 硬件IIC | 软件模拟IIC |

|---|---|---|

| CPU占用率 | 极低(DMA/中断驱动) | 较高(轮询+延时控制) |

| 时序精度 | 高(由波特率发生器精确控制) | 依赖延时函数精度 |

| 可配置性 | 固定模式(标准/快速) | 完全可编程 |

| 抗干扰能力 | 强(内置滤波与噪声抑制) | 依赖外部电路与代码健壮性 |

| 开发复杂度 | 中等(需配置寄存器) | 高(需手动实现完整协议) |

| 支持多主竞争 | 是(支持仲裁) | 否(需额外逻辑模拟) |

| 最大通信速率 | ≤400 kbps | 通常≤100 kbps(受GPIO切换速度限制) |

从上表可见,软件模拟IIC牺牲了性能与实时性,但换来了 引脚灵活性和协议可控性 ,适用于调试、兼容性适配或小批量数据传输场景。

5.2 GPIO控制下的软件IIC实现机制

在RA6T2上实现软件IIC,核心是通过FSP库或直接寄存器操作控制SCL和SDA引脚状态。以下为关键步骤与代码示例:

// 定义IIC引脚(假设P404=SCL, P405=SDA)

#define IIC_SCL_PORT R_PFS->PORT[4].PIN[4]

#define IIC_SDA_PORT R_PFS->PORT[4].PIN[5]

// 输出模式设置(开漏)

void iic_gpio_init(void) {

IIC_SCL_PORT.PMR = 0; // 禁用外设功能

IIC_SCL_PORT.PDR = 1; // 输出模式

IIC_SCL_PORT.NOD = 1; // 开漏输出

IIC_SCL_PORT.PSR = 0;

IIC_SDA_PORT.PMR = 0;

IIC_SDA_PORT.PDR = 1;

IIC_SDA_PORT.NOD = 1;

IIC_SDA_PORT.PSR = 0;

// 外部上拉电阻必须存在(一般4.7kΩ)

}

软件IIC起始条件生成逻辑

void iic_start_condition(void) {

__disable_irq(); // 关中断防止被打断

// SDA高→低,SCL保持高

set_sda_low();

delay_us(5);

set_scl_low(); // 拉低SCL进入准备状态

delay_us(5);

__enable_irq();

}

void set_sda_low(void) {

IIC_SDA_PORT.PODR = 0;

}

void set_sda_high_input(void) {

IIC_SDA_PORT.PDR = 0; // 输入模式模拟浮空

}

参数说明 :

-delay_us():基于SysTick或R_BSP_SoftwareDelay()实现微秒级延时;

- 关中断确保时序不被破坏,尤其在发送地址帧期间;

- SDA切换为输入模式用于检测ACK/NACK。

数据位传输函数(MSB优先)

uint8_t iic_write_byte(uint8_t data) {

for (int i = 7; i >= 0; i--) {

set_scl_low();

delay_us(2);

if (data & (1 << i))

set_sda_high_input();

else

set_sda_low();

delay_us(2);

set_scl_high(); // 上升沿采样

delay_us(5);

}

// 读取ACK:主机释放SDA,从机拉低表示ACK

set_scl_low();

delay_us(2);

set_sda_high_input(); // 释放SDA

delay_us(2);

set_scl_high();

delay_us(3);

uint8_t ack = IIC_SDA_PORT.PIR; // 读取SDA电平

set_scl_low();

return ack == 0 ? 0 : 1; // 0=ACK, 1=NACK

}

5.3 抗干扰设计与PCB布局建议

工业环境中电磁干扰(EMI)可能导致IIC通信异常。以下是提升稳定性的系统级措施:

PCB布线原则(推荐)

| 措施 | 说明 |

|---|---|

| SCL/SDA走线尽量短 | <10cm,减少天线效应 |

| 平行布线并靠近GND层 | 控制阻抗,降低串扰 |

| 使用差分对思路布线 | 即使非差分信号也应紧耦合 |

| 添加TVS二极管(如SM712) | 抑制±15kV ESD冲击 |

| 加磁珠隔离电源 | 如BLM18AG900SN1D,滤除高频噪声 |

| 去耦电容就近放置 | 每个IC旁加0.1μF + 10μF陶瓷电容 |

graph TD

A[MCU RA6T2] -->|SCL, SDA| B(TVS保护)

B --> C[磁珠隔离]

C --> D[EEPROM芯片]

D --> E[GND Plane]

F[VCC] --> G[10uF钽电容]

G --> H[0.1uF陶瓷电容]

H --> D

5.4 基于状态机的IIC通信框架设计

为提高代码可维护性和错误恢复能力,建议采用有限状态机(FSM)模型管理IIC事务:

typedef enum {

IIC_IDLE,

IIC_START,

IIC_SEND_ADDR,

IIC_SEND_REG,

IIC_RESTART,

IIC_READ_DATA,

IIC_STOP,

IIC_ERROR

} iic_state_t;

static iic_state_t current_state;

void iic_fsm_task(void) {

switch (current_state) {

case IIC_IDLE:

if (iic_request_pending) {

iic_start_condition();

current_state = IIC_SEND_ADDR;

}

break;

case IIC_SEND_ADDR:

if (iic_write_byte(dev_addr | WRITE)) {

current_state = IIC_ERROR;

} else {

current_state = IIC_SEND_REG;

}

break;

case IIC_SEND_REG:

if (iic_write_byte(reg_addr)) {

current_state = IIC_ERROR;

} else {

if (is_read_op) {

iic_restart();

current_state = IIC_SEND_ADDR;

} else {

current_state = IIC_STOP;

}

}

break;

case IIC_STOP:

iic_stop_condition();

iic_complete_callback();

current_state = IIC_IDLE;

break;

default:

handle_iic_error();

break;

}

}

该状态机可通过定时器调度或RTOS任务定期调用,实现 非阻塞式通信 ,避免长时间占用CPU。

5.5 EEPROM寿命管理与写均衡策略

长期运行中频繁写入会导致EEPROM单元老化。典型耐久性为10万次写周期。为此提出以下优化机制:

写操作统计表(示例10条记录)

| 存储地址 | 累计写入次数 | 最后访问时间(Unix) | 是否标记坏块 |

|---|---|---|---|

| 0x0000 | 87,432 | 1712054321 | 否 |

| 0x0001 | 98,210 | 1712054325 | 否 |

| 0x0002 | 101,567 | 1712054330 | 是(超限) |

| 0x0003 | 45,201 | 1712054332 | 否 |

| 0x0004 | 76,889 | 1712054335 | 否 |

| 0x0005 | 92,100 | 1712054338 | 否 |

| 0x0006 | 67,443 | 1712054340 | 否 |

| 0x0007 | 88,901 | 1712054342 | 否 |

| 0x0008 | 105,001 | 1712054345 | 是(超限) |

| 0x0009 | 34,567 | 1712054348 | 否 |

寿命优化策略

- 写均衡算法 :将频繁更新的数据分散到多个物理地址轮流写入;

- 缓存机制 :RAM中暂存变更,定时批量刷入EEPROM;

- 日志回滚结构 :采用环形日志方式记录变更,避免定点擦写;

- 坏块替换 :当某地址失效时,映射至备用区域并更新索引表;

- CRC32校验 :每次读取验证数据完整性,发现错误可尝试重读或恢复默认值。

这些机制结合看门狗监控与故障自检流程,可显著提升系统在工业现场连续运行数年的可靠性表现。

简介:本文介绍基于瑞萨RA6T2微控制器实现IIC通信协议驱动EEPROM进行数据读写的完整方案。通过配置RA6T2的IIC模块,结合嵌入式C语言编程,实现对EEPROM的字节写入、随机读取和页写操作,确保数据存储的可靠性与稳定性。项目包含硬件连接设计、IIC时序配置、软件驱动编写及调试方法,适用于工业控制、智能仪表等需要非易失性存储的应用场景。代码经过实测可直接集成到实际工程中,具备良好的可移植性和扩展性。

openvela 操作系统专为 AIoT 领域量身定制,以轻量化、标准兼容、安全性和高度可扩展性为核心特点。openvela 以其卓越的技术优势,已成为众多物联网设备和 AI 硬件的技术首选,涵盖了智能手表、运动手环、智能音箱、耳机、智能家居设备以及机器人等多个领域。

更多推荐

已为社区贡献28条内容

已为社区贡献28条内容

所有评论(0)