FPGA PCI代码模块详解:完整代码及详细注释,助力开发者高效构建通信系统

本PCI Target参考设计是一套基于Verilog语言开发的32位33MHz PCI目标设备解决方案,适用于Cyclone III系列FPGA(具体型号为EP3C5F256C6)。该设计遵循PCI规范,实现了PCI总线的配置、地址解码、数据传输、奇偶校验等核心功能,同时提供了与后端设备(如SDRAM、SRAM、FIFO或I/O设备)的接口,可作为嵌入式系统中PCI总线通信的基础模块。FPGAp

FPGA pci代码,模块完整,注释完整

一、设计概述

本PCI Target参考设计是一套基于Verilog语言开发的32位33MHz PCI目标设备解决方案,适用于Cyclone III系列FPGA(具体型号为EP3C5F256C6)。该设计遵循PCI规范,实现了PCI总线的配置、地址解码、数据传输、奇偶校验等核心功能,同时提供了与后端设备(如SDRAM、SRAM、FIFO或I/O设备)的接口,可作为嵌入式系统中PCI总线通信的基础模块。

FPGA pci代码,模块完整,注释完整

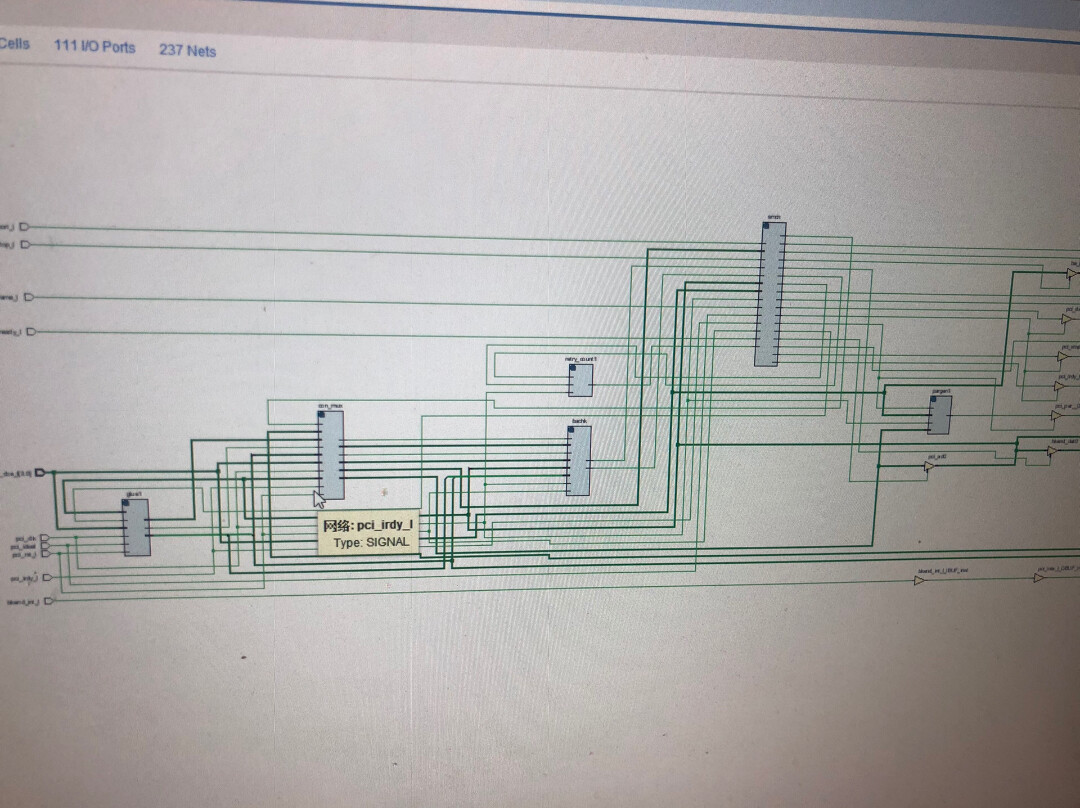

设计包含12个核心模块及配套的工程配置文件,模块间通过标准化接口协同工作,覆盖了PCI目标设备从总线交互到后端数据处理的全流程。整体架构采用分层设计思想,将PCI协议处理、地址管理、数据缓冲、奇偶校验等功能解耦,具备良好的可扩展性和可维护性,工程师可根据实际后端设备需求,通过修改配置参数快速适配不同应用场景。

二、核心模块功能解析

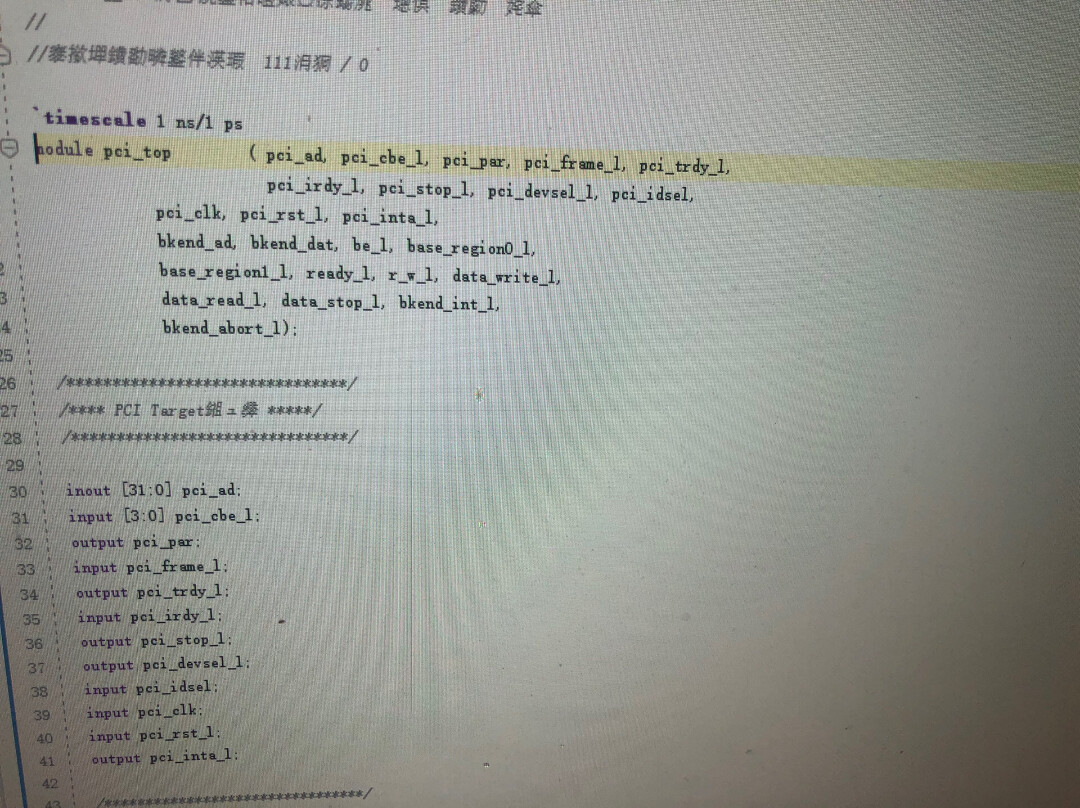

2.1 顶层模块(pci_top.v)

作为整个设计的入口,pci_top模块承担模块实例化、信号连接与I/O管理的核心职责,是PCI总线与后端设备交互的“桥梁”。其主要功能包括:

- 模块集成:实例化

statemachine(状态机)、pargen(奇偶校验)、configmux(配置寄存器与数据多路复用)、baseaddrchk(基地址检查)等核心子模块,构建完整的PCI Target功能链路。 - I/O环管理:实现PCI总线信号(如

pciad、pcicbel、pcipar)与后端设备信号(如bkendad、bkenddat)的三态缓冲控制,确保信号在不同传输阶段的正确驱动与高阻态切换。 - 信号分发:将PCI总线的时钟(

pciclk)、复位(pcirstl)等全局信号分发至各子模块,同时将子模块的控制信号(如地址命中信号hitba0l/hitba1l)、数据信号(如pcidat_out)按需连接,保障模块间数据与控制流的顺畅。

该模块的关键设计在于I/O信号的时序匹配与驱动控制,需严格遵循PCI规范中11ns的Tco(时钟到输出)时序要求,确保总线交互的稳定性。

2.2 基地址检查模块(base_addr_chk.v)

baseaddrchk模块是PCI地址解码的核心,负责管理基地址寄存器(BA0、BA1)并判断PCI总线地址是否命中后端设备的地址空间,其核心功能如下:

- 基地址寄存器管理:

- 实现BA0和BA1寄存器的只写功能,系统软件可通过配置周期将分配的基地址写入寄存器(通过ba0en/ba1en时钟使能信号触发)。

- 复位时将BA0、BA1初始化为0,确保上电后地址解码的初始状态稳定。 - 地址命中判断:

- 接收来自configmux模块的地址空间大小参数(ba0size/ba1size),该参数由工程师根据后端设备需求配置(如1MB空间对应ba0size=28'hFFF0000)。

- 通过地址掩码运算(pciaddr & ba0size == ba0)判断当前PCI地址是否落在BA0/BA1对应的地址区域,输出低电平有效的命中信号(hitba0l/hitba1l),为状态机触发devsel_l(设备选择)信号提供依据。

地址解码逻辑采用“掩码匹配”思想,仅对地址空间的有效位进行比较,无关位(低位0)通过掩码屏蔽,确保地址判断的准确性与灵活性。

2.3 后端守护模块(bkend_daemon.v)

bkend_daemon模块是后端设备的行为模型,负责仲裁PCI与后端设备间的信号交互,模拟不同场景下的数据传输响应,其核心功能包括:

- 后端存储管理:

- 内置两个64×32bit的存储银行(bk0、bk1),用于模拟后端存储设备(如SRAM),支持数据的读写操作。

- 初始化阶段将存储银行清零,确保测试环境的初始数据一致性。 - 数据传输仲裁:

- 正常场景:对bk0的所有读写操作均正常响应,通过readyl信号告知PCI状态机“后端就绪”,支持突发传输(Burst)。

- 特殊场景:针对bk1的特定地址(如20'h000A0~20'h000E0)设计差异化响应,模拟PCI协议中的异常处理流程:

- 地址20'h000A0:不响应readyl,触发数据重试(Retry)。

- 地址20'h000B0:置位datastopl,触发数据停止(Data Stop)。

- 地址20'h000C0:置位bkendabortl,触发事务中止(Abort)。

- 地址20'h000D0/20'h000E0:控制bkendintl,实现中断的使能与禁用。 - 状态机控制:采用

idle→firstdata→ready→datastop/data_abort的状态流转,确保数据传输的时序正确性,支持突发传输中的地址自增(每次+4字节)。

该模块的设计价值在于提供了完整的PCI事务异常场景模拟,可用于验证PCI Target对重试、中止、中断等协议特性的支持,降低实际硬件测试的复杂度。

2.4 配置多路复用模块(config_mux.v)

config_mux模块是PCI配置空间的核心实现,同时负责PCI数据总线的输出多路复用,其核心功能分为两部分:

- PCI配置寄存器实现:

- 定义只读配置寄存器参数,包括设备ID(DEVICEID=16'h0120)、厂商ID(VENDORID=16'h1022,AMD)、类代码(CLASSCODE=24'h058000,内存控制器)、基地址空间配置(BA0为I/O类型、BA1为内存类型,均为1MB空间)等,工程师可根据实际设备修改这些参数。

- 实现配置寄存器的读写控制:写操作时根据pciaddr(配置地址)触发对应寄存器的使能信号(如写8'h10地址触发ba0en);读操作时根据地址输出对应寄存器的值(如读8'h00地址返回{DEVICEID, VENDOR_ID})。 - 数据输出多路复用:

- 控制PCI数据总线(pcidatout)的输出源:配置周期(cfgout=1)时输出配置寄存器数据(cfgdatout),正常数据周期(cfgout=0)时输出后端设备数据(bkend_dat),确保数据总线在不同事务类型下的正确切换。

配置寄存器的实现严格遵循PCI规范,确保操作系统或PCI总线枚举软件能正确识别设备类型、地址空间需求等关键信息,是设备接入PCI总线的“身份标识”。

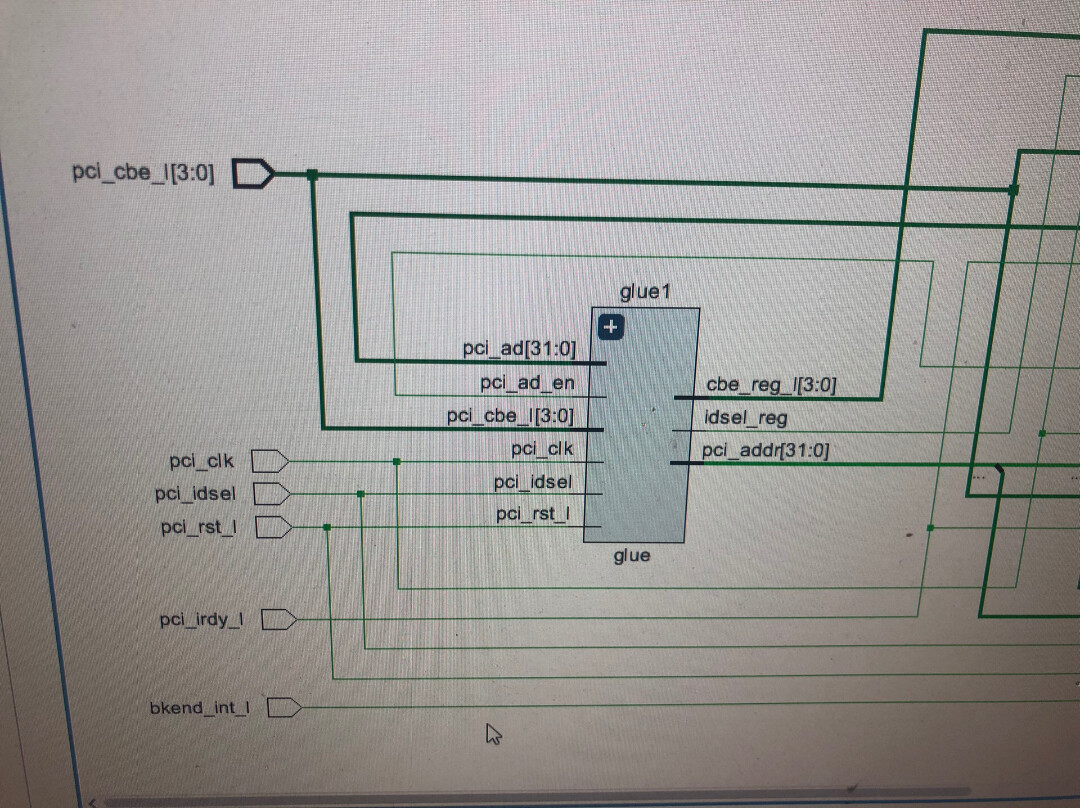

2.5 胶合逻辑模块(glue.v)

glue模块承担信号时序调理与寄存功能,为PCI事务的地址阶段与数据阶段提供稳定的信号支持,其核心功能如下:

- 地址与控制信号寄存:

- 在PCI事务的地址阶段(由pciaden使能),将pciad(地址/数据总线)中的地址信息寄存到pciaddr,同时寄存pcicbel(命令/字节使能)和pciidsel(初始化设备选择)信号。

- 寄存后的信号(pciaddr、cberegl、idsel_reg)为后续的地址解码、配置寄存器访问提供稳定的输入,避免地址阶段与数据阶段的信号冲突。 - 复位控制:复位时将所有寄存信号清零,确保上电后模块的初始状态一致。

该模块的设计意义在于解决PCI总线“地址/数据复用”特性带来的信号时序问题,通过寄存隔离地址阶段与数据阶段的信号,提升系统的时序稳定性。

2.6 奇偶校验生成模块(pargen.v)

pargen模块负责生成PCI总线的奇偶校验位(pci_par),确保数据传输的完整性,其核心功能如下:

- 奇偶校验计算:

- 对PCI数据总线(pcidatout)按字节分割(31:24、23:16、15:8、7:0),分别计算每个字节的异或值(par3~par0)。

- 同时计算pcicbel信号的异或值(cbereg),最终通过组合逻辑生成整体的奇偶校验位(parout),遵循PCI规范的“偶校验”要求。 - 流水线设计:

- 在pci_clk上升沿触发校验计算,确保校验位的生成与数据输出时序匹配,满足PCI规范中11ns的Tco时序要求,避免因校验计算延迟导致的总线错误。 - 输出使能控制:仅在

paroe(奇偶校验输出使能)为1时驱动parout,否则置为高阻态,符合PCI总线的三态控制逻辑。

奇偶校验是PCI总线可靠性的关键保障,该模块通过流水线与组合逻辑结合的设计,在确保时序合规的同时,实现了高效的校验计算。

2.7 时钟复位模块(pci_clk_reset.v)

pciclkreset模块是测试环境的辅助模块,负责生成PCI时钟与复位信号,其核心功能如下:

- 时钟生成:通过

always块生成周期可配置的时钟(默认period=30ns,对应33MHz),满足PCI规范的时钟频率要求。 - 复位生成:初始化时置位复位信号(

resetl=0),并在resettime=120ns后释放复位(reset_l=1),确保所有模块在时钟稳定后进入正常工作状态。

该模块主要用于仿真环境,为整个设计提供稳定的时钟与复位激励,避免因外部激励不稳定导致的仿真误差。

2.8 测试激励模块(pci_stim.v)

pci_stim模块是PCI总线的主设备仿真模型,负责生成PCI事务激励并验证Target的响应,其核心功能如下:

- 测试用例覆盖:

- 配置周期测试:读写PCI配置寄存器(如设备ID、基地址寄存器),验证配置空间的正确性。

- 正常数据传输测试:对BA0、BA1地址区域执行突发/非突发读写,验证正常数据传输流程。

- 异常场景测试:触发重试、停止、中止、中断等异常事务,验证Target的异常处理能力。 - 事务状态判断:通过

checkcycle任务监控devsell、trdyl、stopl等信号,判断事务的完成状态(如数据传输成功、重试、中止),并统计测试错误数量。 - 奇偶校验验证:计算发送数据的奇偶校验位,与Target返回的

pci_par信号比较,验证校验功能的正确性。

该模块是设计验证的核心,通过自动化测试用例覆盖PCI Target的核心功能,确保设计符合PCI规范与实际应用需求。

2.9 测试平台模块(pci_tb.v)

pci_tb是整个设计的仿真顶层,负责实例化测试环境与待测试模块,构建完整的仿真链路:

- 模块实例化:

- 实例化pciclkreset(时钟复位)、pcistim(测试激励)、bkenddaemon(后端守护)与pci_top(待测试Target)。

- 连接各模块的信号(如PCI总线信号、后端设备信号),确保激励能正确传递到Target,Target的响应能被测试模块捕获。 - 仿真模式控制:通过

ifdef GATE宏定义支持RTL仿真与门级仿真切换,门级仿真时加载FPGA网表(pci_top.vo),验证时序与布局布线后的功能正确性。

该模块为设计提供了标准化的仿真入口,工程师可直接运行该模块启动仿真,无需手动搭建复杂的信号连接。

三、工程配置文件说明

3.1 Quartus工程文件(pci_top.qpf/.qsf)

- pci_top.qpf:工程主文件,记录Quartus版本(16.1)、工程创建时间等基础信息,是Quartus Prime软件识别工程的入口。

- pci_top.qsf:工程配置文件,核心配置包括:

- 器件配置:指定目标FPGA为Cyclone III系列的EP3C5F256C6。

- 文件管理:添加所有Verilog源文件(如

statemachine.v、configmux.v)与测试文件(如pci_tb.v)。 - 仿真配置:指定仿真工具为ModelSim-Altera,设置时间精度为1ps,关联测试平台(

pci_tb)。 - 时序约束:默认未添加自定义约束,工程师需根据实际硬件需求补充时钟周期、输入延迟、输出延迟等约束。

3.2 门级仿真文件(pci_top.vo)

pci_top.vo是FPGA综合后的门级网表文件,包含:

- 器件原语实例化(如Cyclone III的IO缓冲

cycloneiiiioobuf、寄存器dffeas、组合逻辑单元cycloneiiilcellcomb)。 - 信号连接信息:记录RTL代码综合后的实际硬件连接,门级仿真时可验证时序与布局布线对功能的影响。

- SDF注释:包含时序信息注释(

$sdfannotate("pcitop_v.sdo")),支持时序仿真,验证设计是否满足时序要求。

3.3 ModelSim配置文件(modelsim.ini)

modelsim.ini是ModelSim仿真工具的配置文件,核心配置包括:

- 库路径配置:指定工作库(

work)与Altera器件原语库的路径,确保仿真时能正确加载器件模型。 - 仿真参数配置:设置仿真分辨率(

Resolution=ps)、默认运行时间(RunLength=100)、断言处理(BreakOnAssertion=3,断言失败时停止仿真)。 - 编译选项:配置Verilog/VHDL的编译参数(如Verilog的

NoDebug=0,保留调试信息)。

四、设计工作流程

4.1 设计阶段

- 需求分析:明确后端设备类型(如I/O、内存)、地址空间大小、传输速率等需求,确定PCI配置参数(如设备ID、类代码、基地址空间类型)。

- 模块开发:基于需求修改核心模块的参数(如

configmux.v中的BA0/BA1地址空间配置、baseaddr_chk.v的地址掩码),无需修改模块的核心逻辑。 - 工程配置:在Quartus中打开

pcitop.qpf,确认器件型号、文件路径是否正确,添加时序约束(如createclock -name pciclk -period 30 [getports pci_clk])。

4.2 仿真验证阶段

- RTL仿真:

- 运行pcitb.v启动RTL仿真,pcistim自动执行测试用例,覆盖配置、正常数据传输、异常场景。

- 查看仿真日志,确认测试错误数量为0,验证功能正确性。 - 门级仿真:

- 综合工程生成门级网表(pcitop.vo),在pcitb.v中定义GATE宏,启动门级仿真。

- 验证时序与布局布线后的功能是否正常,重点关注时钟到输出(Tco)、建立时间(Setup)与保持时间(Hold)是否满足要求。

4.3 硬件实现阶段

- 综合与布局布线:在Quartus中执行综合与布局布线,生成FPGA配置文件(.sof或.pof)。

- 硬件下载:通过USB-Blaster等下载工具将配置文件烧录到Cyclone III FPGA,完成硬件实现。

- 硬件测试:使用PCI总线分析仪或操作系统工具(如Windows的设备管理器、Linux的lspci命令)验证设备是否被正确识别,通过应用程序测试数据传输功能。

五、关键设计亮点与注意事项

5.1 设计亮点

- 模块化设计:各模块功能单一、接口标准化,如

configmux仅负责配置与数据复用,baseaddr_chk仅负责地址解码,便于维护与复用。 - PCI规范合规:严格遵循PCI 2.1规范,支持配置周期、正常数据周期、突发传输、重试、中止、中断等核心特性,确保与主流PCI主设备(如CPU、PCI桥)兼容。

- 可扩展性强:通过修改

configmux的参数即可适配不同后端设备(如将BA0的地址空间从1MB改为4MB),无需修改核心逻辑;bkenddaemon可替换为实际后端设备的控制逻辑,快速实现硬件对接。 - 完善的验证体系:

pcistim覆盖PCI Target的核心功能与异常场景,pcitb支持RTL与门级仿真,确保设计在不同阶段的正确性。

5.2 注意事项

- 时序约束:工程默认未添加完整的时序约束,硬件实现前需补充时钟约束、输入/输出延迟约束,避免时序违规导致硬件功能异常。

- 基地址配置:

configmux中BA0/BA1的地址空间类型(IOON/MEMON)与大小(如ADDR1M)需根据后端设备实际需求修改,错误配置会导致PCI总线枚举失败。 - 中断处理:后端设备触发中断时需确保

bkendintl信号的时序正确性,避免中断信号不稳定导致PCI主设备无法正确响应。 - 奇偶校验:PCI总线要求必须启用奇偶校验,

pargen模块的输出使能(par_oe)需与数据输出同步,否则会导致总线错误。

六、总结与扩展建议

本PCI Target参考设计是一套功能完整、合规性强的解决方案,覆盖了PCI总线目标设备的核心功能,可作为嵌入式系统中PCI通信的基础模块。通过仿真验证与硬件实现,该设计能稳定支持与PCI主设备的交互,满足I/O设备、内存控制器等后端设备的通信需求。

扩展建议

- 性能优化:当前设计为33MHz,若需支持66MHz PCI总线,需修改时钟周期(

period=15ns)并优化时序约束,确保关键路径(如地址解码、数据复用)的延迟满足要求。 - 多基地址支持:当前仅支持2个基地址(BA0、BA1),可扩展

baseaddrchk与config_mux模块,增加BA2~BA5,支持更多后端设备的地址空间。 - DMA功能集成:当前设计仅支持Target模式,可集成DMA控制器模块,实现从后端设备到PCI主设备的直接数据传输,提升大数据量传输效率。

- PCIe升级:若需支持更高带宽,可基于该设计的架构思想,开发PCIe Target参考设计,替换PCI总线协议为PCIe协议,适配现代高速通信需求。

通过以上扩展,该设计可广泛应用于工业控制、数据采集、通信设备等领域,为PCI总线相关的嵌入式开发提供高效、可靠的技术支撑。

openvela 操作系统专为 AIoT 领域量身定制,以轻量化、标准兼容、安全性和高度可扩展性为核心特点。openvela 以其卓越的技术优势,已成为众多物联网设备和 AI 硬件的技术首选,涵盖了智能手表、运动手环、智能音箱、耳机、智能家居设备以及机器人等多个领域。

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)