Altium Designer全面学习资料与实战指南

Altium Designer 是一款集原理图设计、PCB布局布线、3D建模与仿真于一体的高端电子设计自动化(EDA)工具,广泛应用于消费电子、工业控制、通信设备及嵌入式系统等领域。其强大的集成环境支持从概念到生产的全流程开发,尤其适用于复杂多层板和高密度互连(HDI)设计。通过统一的数据模型,实现原理图与PCB的实时同步,提升设计效率与准确性,已成为5年以上经验工程师进行中高端硬件开发的首选平台

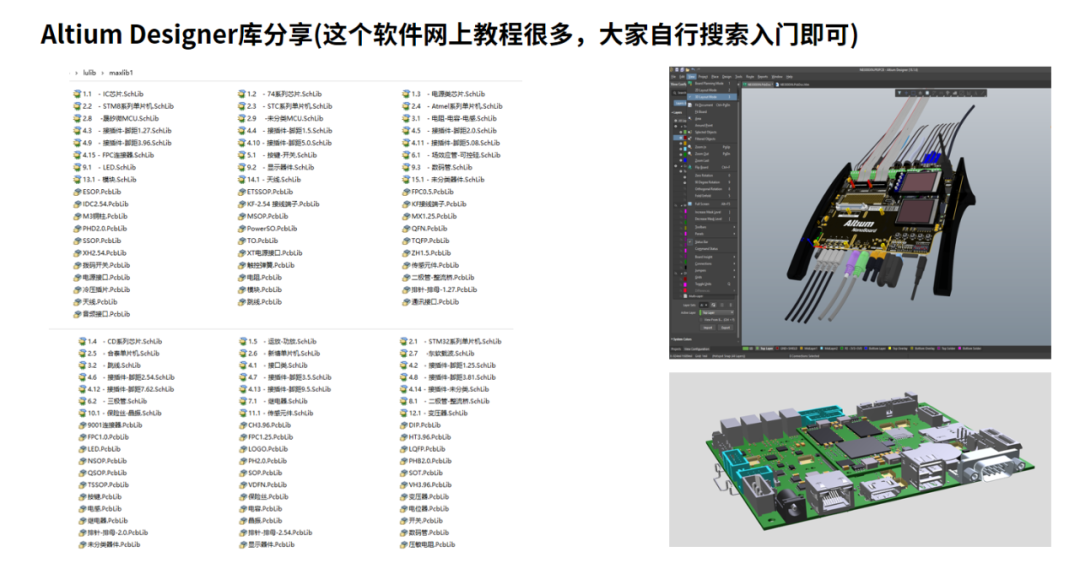

简介:Altium Designer是一款广泛应用于电子设计领域的强大PCB设计软件,集成了电路原理图设计、PCB布局、3D查看、信号完整性分析和项目管理等核心功能。本学习资料包内容系统完整,涵盖从基础操作到高级设计的全流程知识,包含教程、示例项目与参考手册,帮助用户掌握元件库管理、原理图绘制、PCB布线规则、仿真分析及制造文件输出等关键技能,适合初学者和进阶用户提升电子设计能力。

1. Altium Designer软件简介与应用场景

Altium Designer 是一款集原理图设计、PCB布局布线、3D建模与仿真于一体的高端电子设计自动化(EDA)工具,广泛应用于消费电子、工业控制、通信设备及嵌入式系统等领域。其强大的集成环境支持从概念到生产的全流程开发,尤其适用于复杂多层板和高密度互连(HDI)设计。通过统一的数据模型,实现原理图与PCB的实时同步,提升设计效率与准确性,已成为5年以上经验工程师进行中高端硬件开发的首选平台。

2. 软件界面与基本操作入门

2.1 Altium Designer的启动与项目结构

2.1.1 软件安装与授权配置

Altium Designer作为电子设计自动化(EDA)领域的旗舰级工具,其功能强大且高度集成,支持从原理图设计、PCB布局布线到3D建模和制造输出的全流程开发。在正式进入设计流程之前,正确完成软件的安装与授权配置是确保后续工作顺利进行的基础。

Altium Designer的安装过程通常分为两个阶段:软件本体安装和许可证激活。推荐使用官方提供的安装程序(如Altium Designer Installer),该程序集成了必要的运行环境(如.NET Framework、DirectX等)并自动处理依赖项。安装路径建议选择非系统盘目录,例如 D:\Altium\AD23 ,以避免权限问题和便于后期维护。

安装完成后,首次启动时会弹出“License Management”窗口,用户需根据企业或个人使用情况选择合适的授权模式:

| 授权类型 | 说明 | 适用场景 |

|---|---|---|

| Standalone License | 单机授权,绑定特定机器 | 个人开发者、小型团队 |

| Network License | 网络浮动授权,通过服务器分发 | 多人协作、企业级部署 |

| Subscription License | 基于云的订阅制授权 | 需要持续更新功能的用户 |

授权配置的关键在于获取有效的 .alf 或 .lic 文件。对于网络授权,需确保客户端能正常访问 License Server(默认端口 27000),可通过以下命令测试连通性:

ping license-server.company.com

telnet license-server.company.com 27000

若连接失败,应检查防火墙设置或联系IT部门开放相应端口。

在Altium Designer内部,授权管理可通过 Main Menu > Help > Licensing 进入。成功加载后,状态栏将显示当前激活的功能模块(如 PCB, FPGA, Simulation 等)。值得注意的是,部分高级功能(如差分对布线、高速仿真)需要额外购买插件包才能启用。

为了提升稳定性,建议关闭不必要的后台服务(如 Windows Defender 实时扫描),并在 BIOS 中开启 XHCI Hand-off 和禁用 Secure Boot,以防 USB 加密狗识别异常。

此外,Altium 提供了“试用模式”,允许新用户在无许可证情况下体验全部功能 30 天。此模式下所有设计均可保存,但到期后必须输入有效许可方可继续编辑。

graph TD

A[开始安装] --> B[运行Altium Installer]

B --> C{选择安装组件}

C --> D[安装核心平台]

C --> E[可选: 安装Simulators]

C --> F[可选: 安装FPGA Tools]

D --> G[启动License Manager]

G --> H{选择授权方式}

H --> I[Standalone: 导入.alf文件]

H --> J[Network: 输入Server地址]

H --> K[Subscription: 登录账户]

I --> L[验证硬件加密狗/Soft-key]

J --> L

K --> L

L --> M[启动主界面]

上述流程图清晰展示了从安装到授权的完整路径。每一步都可能影响最终可用性,尤其是当使用硬件加密狗(USB Dongle)时,驱动兼容性问题较为常见。此时可尝试以管理员身份运行“HaspUserSetup.exe”重新安装 Sentinel 驱动。

参数说明:

- .alf 文件:用于离线生成授权请求,包含主机唯一标识(Host ID)

- .lic 文件:由Altium签发的实际授权证书,包含有效期和功能列表

- Host ID:通常基于网卡MAC地址生成,更换网卡可能导致授权失效

综上所述,正确的安装与授权不仅是技术操作,更是保障设计连续性的前提。尤其在企业环境中,统一部署策略和集中式授权管理可显著降低运维成本。

2.1.2 创建新项目与文件类型解析

在Altium Designer中,“项目”(Project)是一个逻辑容器,用于组织相关的原理图、PCB、库文件及其他辅助文档。一个典型的电子产品设计项目通常包括多个文件类型,彼此通过编译机制关联,形成完整的工程体系。

创建新项目的标准流程如下:

- 启动Altium Designer主界面;

- 选择 File > New > Project ;

- 在“New Project”对话框中选择项目类型(如 PCB Project);

- 设置项目名称(如

PowerSupply_Design.PrjPcb); - 指定存储路径,建议为每个项目建立独立目录;

- 点击“Create”完成初始化。

此时,项目管理器(Projects Panel)中会出现一个新的 .PrjPcb 文件,代表一个PCB工程项目。右键该项目可添加多种子文件:

| 文件类型 | 扩展名 | 功能描述 |

|---|---|---|

| 原理图文件 | .SchDoc | 绘制电路逻辑连接 |

| PCB文件 | .PcbDoc | 物理板图设计与布线 |

| 原理图库 | .SchLib | 存放自定义元件符号 |

| 封装库 | .PcbLib | 定义元件物理外形 |

| 集成库 | .IntLib | 合并符号与封装的单一文件 |

| 脚本文件 | .Bas/.Pas | 自动化任务脚本 |

| 文档模板 | .SchDot/.PcbDot | 标准化图纸格式 |

这些文件并非孤立存在,而是通过“编译”过程建立电气连接关系。例如,原理图中的每个元件必须具有唯一的“Designator”(如 U1, R1)和“Footprint”属性,指向PCB库中的具体封装。

以下是一个典型项目结构示例:

/Project_Root/

├── PowerSupply.PrjPcb # 主项目文件

├── Main_Circuit.SchDoc # 主原理图

├── Control_Section.SchDoc # 控制模块子图

├── PowerSupply.PcbDoc # 对应PCB文件

├── CustomComponents.SchLib # 自定义符号库

├── Package_Libraries.PcbLib # 封装库

└── Outputs/ # 输出目录

├── Gerber/

├── BOM.csv

└── Assembly_PDF/

项目结构的设计直接影响后期维护效率。推荐采用模块化划分原则,将复杂系统拆分为若干功能块(Functional Blocks),并通过“层次化设计”(Hierarchical Design)实现跨图连接。

在添加原理图文件后,可通过双击打开编辑器。Altium 的多标签界面支持同时查看多个文件,极大提升了工作效率。每个文件底部的状态栏会显示当前单位(Imperial/ Metric)、栅格大小(Snap Grid)以及工作层(Current Layer)。

特别注意的是,Altium 使用“项目范围变量”(Project-Level Variables)来统一管理参数,如版本号、公司名称等。这些变量可在 Project Options > Parameters 中定义,并在标题块中引用,确保信息一致性。

代码示例:如何通过脚本批量创建项目文件(使用DelphiScript)

procedure CreateNewProject;

var

ProjectPath : WideString;

ProjectName : WideString;

Project : IProject;

begin

ProjectPath := 'D:\AD_Projects\NewDesign';

ProjectName := 'SensorNode.PrjPcb';

// 创建项目对象

Project := CreateProject(ProjectPath + '\' + ProjectName, ePcbProject);

if Project <> nil then

begin

AddDocumentToProject(Project, 'Main.SchDoc', eSCHDocument);

AddDocumentToProject(Project, 'Layout.PcbDoc', ePCBDocument);

ShowMessage('项目创建成功!');

end

else

ShowMessage('创建失败,请检查路径权限');

end;

逻辑分析:

- 第1–4行:声明变量类型, WideString 支持Unicode路径;

- 第6–7行:设定项目路径与名称;

- 第9行:调用 CreateProject 函数,传入路径和项目类型常量 ePcbProject ;

- 第11–18行:判断是否创建成功,若成功则添加原理图和PCB文件;

- AddDocumentToProject 是内置API,用于将指定类型的文档加入项目;

- 最终弹出提示框反馈结果。

该脚本可用于自动化项目初始化,尤其适合标准化产品线开发。执行前需在 Run Script 对话框中加载 .pas 文件。

综上,合理规划项目结构不仅有助于团队协作,也为后续的版本控制(如Git/SVN集成)打下基础。良好的命名规范、目录层级和文件分类习惯,是专业级PCB设计的基本素养。

2.1.3 项目管理器的使用与组织结构

项目管理器(Projects Panel)是Altium Designer中最核心的导航工具之一,位于界面左侧,默认折叠显示。它以树状结构呈现当前工作区内的所有项目及其组成文件,提供直观的组织视图和快捷操作入口。

展开一个典型项目的节点,可见如下结构:

Projects

└── MyAmplifier.PrjPcb [Active]

├── Source Documents

│ ├── Amplifier_Schematic.SchDoc

│ └── PCB_Layout.PcbDoc

├── Libraries

│ ├── Discrete.Lib

│ └── MCU_Family.IntLib

├── Outputs

│ └── OutputJob1.OutJob

└── Project Outputs for MyAmplifier

├── Gerber Files

├── NC Drill

└── BOM Report

其中,“[Active]”表示该项目已被设为当前活动项目,所有操作均作用于此上下文中。右键菜单提供了丰富的管理功能:

- Compile Document/Project :触发电气规则检查(ERC)和网络表生成;

- Add New to Project :添加新文件(如Verilog、Text File);

- Remove from Project :仅移除引用,不删除磁盘文件;

- Open in Explorer :定位到实际存储路径;

- Show on Physical Tab :切换至文件对应的编辑窗口。

项目管理器还支持多项目协同工作。例如,在开发系列产品时,可将多个 .PrjPcb 文件同时加载至同一工作区,便于复用共用库或对比设计差异。

更进一步地,Altium 支持“工作区”(Workspace)概念,允许将多个相关项目打包为一个解决方案(Solution),类似于Visual Studio的.sln文件。这在大型嵌入式系统开发中尤为有用,例如:

- 主控板项目

- 电源模块项目

- 通信接口项目

三者可统一纳入一个 .DsnWrk 工作区文件中,实现全局搜索、交叉探测和统一发布管理。

表格:项目管理器常用操作与快捷键对照

| 操作 | 鼠标操作 | 快捷键 | 说明 |

|---|---|---|---|

| 编译项目 | 右键 → Compile PCB Project | Ctrl+F9 | 生成网络表并检查错误 |

| 添加现有文件 | 右键 → Add Existing to Project | N/A | 支持批量导入 |

| 新建原理图 | 右键Source Docs → Add New to Project → Schematic | Ctrl+N | 自动生成空白.SchDoc |

| 切换活动项目 | 点击项目名 → Set as Active Project | Alt+数字键 | 最多支持9个项目快速切换 |

| 查看编译报告 | 双击Messages面板条目 | F2 | 定位错误位置 |

此外,项目管理器与“消息面板”(Messages Panel)深度联动。一旦编译失败,错误信息将以红色图标形式出现在对应文件旁,点击即可跳转至问题源头。

值得一提的是,Altium 的“项目选项”(Project Options)对话框提供了精细的配置能力。例如:

- 设计规则继承:允许子项目继承父项目的布线规则;

- 输出路径设置:自定义Gerber、钻孔文件的导出目录;

- 版本控制集成:配置SVN/Git仓库地址与提交策略;

- 搜索路径管理:指定第三方库的查找目录,避免“找不到元件”错误。

flowchart LR

A[打开Altium Designer] --> B[加载项目文件.PrjPcb]

B --> C[项目管理器显示结构]

C --> D{是否需要新增文件?}

D -- 是 --> E[右键→Add New to Project]

D -- 否 --> F[直接编辑现有文档]

E --> G[选择文件类型]

G --> H[自动加入编译依赖链]

F --> I[执行Compile Project]

I --> J{是否存在错误?}

J -- 是 --> K[Messages面板高亮提示]

J -- 否 --> L[进入PCB布局阶段]

该流程图揭示了从项目加载到编译验证的完整逻辑链条。每一个环节都依赖项目管理器的准确组织。

最后强调一点:项目文件 .PrjPcb 本质是一个XML格式的清单文件,记录了所有关联文档的相对路径和编译设置。因此,移动项目时务必使用“Save Project As…”而非手动复制文件夹,否则可能导致路径断裂。

总之,熟练掌握项目管理器的使用,不仅能提高工作效率,更能规避因文件丢失或引用错误引发的设计风险。它是连接设计思想与物理实现的第一道桥梁。

3. 电路原理图设计流程与技巧

在现代电子系统开发中,电路原理图不仅是硬件设计的起点,更是整个产品生命周期中信息传递的核心载体。它不仅承载着电气连接关系,还体现了工程师对系统功能、模块划分和可维护性的深层思考。Altium Designer作为业界领先的EDA工具之一,提供了高度集成且灵活的原理图设计环境,支持从简单单板到复杂多层系统的全流程开发。本章将深入探讨原理图设计的理论基础、实际操作技巧以及验证机制,帮助具备五年以上经验的工程师提升设计质量与团队协作效率。

3.1 原理图设计的理论基础

电路原理图的设计远不止是“画线连元件”那么简单。一个高质量的原理图应具备清晰的功能表达、良好的可读性、易于维护的结构,并为后续PCB布局布线提供准确无误的数据支撑。这就要求设计者在动手绘制之前,先建立扎实的理论框架,理解设计背后的逻辑架构与工程规范。

3.1.1 电路功能抽象与模块划分原则

在大型项目中,直接绘制完整原理图往往会导致图纸臃肿、信号混乱、调试困难。因此,必须采用 功能抽象与模块化设计 的方法,将复杂的系统分解为若干个功能明确、接口清晰的子模块。例如,在设计一款嵌入式控制系统时,可以将其划分为电源管理、主控MCU、通信接口(如UART、I2C)、传感器采集、存储单元等独立模块。

这种划分不仅仅是视觉上的分割,更是一种 设计思维的体现 。每个模块应当具有高内聚、低耦合的特点——即模块内部元件紧密协作完成特定功能,而与其他模块之间通过标准接口进行交互。这样做的好处包括:

- 提高可复用性:某个模块(如DC-DC电源)可在多个项目中重复使用;

- 便于团队协作:不同工程师可并行开发不同模块;

- 简化调试:问题定位更快,只需聚焦于出错模块;

- 支持层次化设计:为后续使用Sheet Symbol和Port建立层级连接打下基础。

为了实现有效的模块划分,建议遵循以下设计流程:

- 需求分析 :明确系统整体功能指标;

- 框图构建 :绘制顶层系统框图,识别主要功能块;

- 接口定义 :确定各模块之间的电气接口(电压、电流、协议类型等);

- 优先级排序 :根据风险或依赖关系决定开发顺序;

- 文档化说明 :为每个模块添加注释或设计说明文件。

这种方式尤其适用于工业控制、医疗设备、航空航天等领域中的高可靠性设计场景。

graph TD

A[系统总体需求] --> B[功能框图]

B --> C[模块划分]

C --> D[电源管理模块]

C --> E[主控处理模块]

C --> F[通信接口模块]

C --> G[传感与执行模块]

D --> H[原理图绘制]

E --> H

F --> H

G --> H

H --> I[编译与ERC检查]

I --> J[生成网络表]

上述流程图展示了从系统需求到模块化原理图设计的基本路径,强调了前期规划的重要性。

此外,在Altium Designer中,可通过创建多个 Schematic Sheets 来分别承载各个模块,再通过 Off-Sheet Connectors 或 Ports + Sheet Entries 实现跨页连接,从而形成完整的系统视图。

3.1.2 原理图符号标准化与可读性规范

符号的标准化是保证原理图长期可维护的关键因素。即便是一个设计精良的电路,如果符号命名混乱、引脚排列随意,也会导致阅读困难甚至误解。为此,行业普遍遵循IEEE 315、IEC 60617等国际标准,并结合企业内部规范制定统一的符号规则。

引脚命名与方向约定

在绘制IC符号时,必须严格遵守引脚命名规范。例如:

- 电源引脚应命名为 VCC , AVDD , DVDD 等,避免使用模糊名称如 PWR ;

- 接地引脚统一使用 GND ,不推荐 AGND , DGND 混用而不加区分;

- 双向数据线建议前缀 IO_ ,输入信号以 IN_ 开头,输出以 OUT_ 结尾;

- 时钟信号统一用 CLK 标识,必要时标注频率范围。

同时,引脚的方向设置(Electrical Type)直接影响ERC(电气规则检查)的结果。常见的电气类型包括:

- Input(输入)

- Output(输出)

- Bidirectional(双向)

- Power(电源)

- Ground(地)

- Passive(无源)

错误地将一个输出引脚设为输入,可能导致ERC无法检测到驱动冲突,埋下隐患。

图纸布局美学与信息密度平衡

优秀的原理图不仅功能正确,还应具备良好的视觉体验。建议遵循以下布局原则:

- 信号流向自左至右、自上而下 :符合人类阅读习惯;

- 同类元件对齐排列 :使用Altium的Align工具保持整齐;

- 网络标签简洁明了 :避免过长或含特殊字符;

- 去耦电容靠近芯片电源引脚放置 :即使在原理图阶段也体现物理布局意图;

- 关键网络加粗或高亮显示 :如复位、时钟等重要信号。

| 规范项 | 推荐做法 | 反例 |

|---|---|---|

| 元件标号 | U1, R1, C5 | U?, Rxx, Cap1 |

| 网络标签 | RESET_N, CLK_24MHz | net123, unnamed_bus |

| 注释说明 | 使用Text Annotation注明功能 | 无任何说明 |

| 层次结构 | 使用Sheet Symbol组织模块 | 所有内容挤在一个页面 |

该表格对比了良好实践与常见反模式,有助于团队建立一致的设计语言。

3.1.3 层次化设计思想与复用性考量

随着产品迭代加快,设计复用已成为提高研发效率的重要手段。Altium Designer支持强大的 层次化设计(Hierarchical Design) 功能,允许将子电路封装成可重复调用的图纸模块。

层次化设计有两种主要模式:

1. Bottom-Up(自底向上) :先设计底层子图,再通过Sheet Symbol引入顶层;

2. Top-Down(自顶向下) :先规划顶层结构,再逐层展开生成子图。

推荐采用Top-Down方式,因为它更符合系统工程的思维方式。具体操作步骤如下:

- 在顶层图纸中插入

Sheet Symbol; - 设置其File Name指向待创建的子图(.SchDoc);

- 双击Sheet Symbol进入子图编辑界面;

- 在子图中定义Port(如

DATA_IN,CTRL_OUT); - 返回顶层,自动产生对应的Sheet Entry,实现信号贯通。

// 示例:层次化设计中的Port定义

Port Name: ADDR[7..0]

I/O Type: Output

Style: Right

此代码段表示在子图中定义了一个8位地址总线输出端口,方向向右,便于与顶层连接。Altium会自动生成同名网络,确保跨层级电气连续性。

层次化设计的优势在于:

- 支持模块复用:同一子图可在多个项目中调用;

- 易于版本控制:子图可单独提交至Git/SVN;

- 提升编译效率:可选择性编译某一层级;

- 便于生成BOM:支持按层级导出物料清单。

对于资深工程师而言,还可结合 Design Reuse Blocks 功能,将已验证的电路块保存为可拖拽模板,极大缩短新产品开发周期。

3.2 实际绘图操作与关键技巧

掌握了理论基础后,接下来进入实际操作阶段。Altium Designer提供了丰富的绘图工具和智能化辅助功能,合理运用这些特性能够显著提升设计效率与准确性。

3.2.1 元件放置、连线与网络标签使用

元件放置是原理图绘制的第一步。在Altium中,可通过Libraries面板搜索所需器件,支持模糊匹配和参数筛选。选中后点击即可放置,支持连续放置模式(双击退出)。

连线(Wire)与网络(Net)的本质区别

初学者常混淆Wire与Net的概念。实际上:

- Wire 是图形元素,仅表示两点间的连线;

- Net 是电气连接实体,由编译器根据Wire、Net Label、Power Port等生成。

这意味着即使没有画线,只要两个引脚连接到相同Net Label,它们就属于同一网络。这一特性可用于简化布线,特别是在高密度电路中。

// 示例:使用Net Label建立隐式连接

Net Label: VCC_3V3

Location: Near pin 1 of U1 and positive terminal of C1

上述代码并非真实代码,而是描述性语句,说明如何通过Net Label替代冗余走线。Altium会在编译时自动识别所有标记为

VCC_3V3的节点为同一网络。

此外,建议启用 Automatic Junction Insertion 功能,当三条及以上Wire交汇时,软件会自动添加Junction(实心圆点),防止连接遗漏。

高级技巧:差分对与总线命名规范

对于高速信号(如USB、LVDS),需使用差分对(Differential Pair)。在原理图中可通过命名约定来标识:

- 正负信号分别命名为 DP 和 DM

- 或使用 _P / _N 后缀,如 CLK_P , CLK_N

Altium支持通过 Designator_Pair 机制识别此类信号,并在PCB阶段自动应用差分布线规则。

3.2.2 总线、端口与层次化图纸连接方法

当涉及多位数据/地址总线时,手动绘制每条线显然不可行。Altium提供 Bus 和 Bus Entry 工具来简化操作。

总线连接语法详解

总线本质上是一个命名集合,其成员通过方括号索引表示。例如:

Bus Name: DATA[15..0]

Connected Wires:

- Wire to D0 → labeled as DATA[0]

- Wire to D1 → labeled as DATA[1]

...

编译后,Altium会生成16个独立网络:

DATA[0],DATA[1], …,DATA[15]。注意方括号必须使用英文格式,否则解析失败。

更进一步,可通过 Bus Definition File (.bdd) 批量定义复杂总线结构,适用于PCIe、SDRAM等接口。

层次化连接实战示例

假设有一个ADC模块需要接入主控系统,其接口包含:

- 数据线: DATA[11..0]

- 控制线: CS_N , RD_N , INT

- 时钟: CONV_CLK

在子图中定义Port如下:

Port DATA[11..0] : Output

Port CS_N : Input

Port RD_N : Input

Port INT : Output

Port CONV_CLK : Output

在顶层图中,Sheet Symbol将自动生成对应Sheet Entry,无需手动绘制连接线。编译后即可形成完整网络映射。

flowchart LR

TopSheet[Top Level Schematic] --> SS[Sheet Symbol: ADC_Module]

SS --> SubSheet[Sub-Schematic: adc_control.SchDoc]

SubSheet --> P1[Port: DATA[11..0]]

SubSheet --> P2[Port: CS_N]

SubSheet --> P3[Port: INT]

TopSheet --> MCU[Microcontroller]

P1 -- Net: DATA[11..0] --> MCU

P2 -- Net: CS_N --> MCU

P3 -- Net: INT --> MCU

该流程图展示了层次化设计中信号如何跨越图纸边界传输,体现了Altium对复杂系统建模的强大支持。

3.2.3 注释、标题块及设计信息标注

完善的文档化是专业设计的重要标志。除了电路本身,还需添加必要的元信息:

- Title Block :包含项目名称、图纸编号、版本号、设计师、日期等;

- Revision History :记录每次修改的内容与责任人;

- Signal Description :对关键网络添加文本说明;

- Compliance Notes :标注安规、EMC相关注意事项。

Altium支持通过 Annotate 功能批量更新元件标号(如R? → R1),并可通过 Output Job File 自动化导出PDF格式图纸,嵌入公司模板。

3.3 设计验证与错误排查

完成原理图绘制后,必须进行系统性验证,确保电气逻辑正确、无潜在冲突。

3.3.1 编译项目与电气规则检查(ERC)

点击菜单 Project > Compile PCB Project 启动编译。成功后打开 Messages 面板查看警告与错误。

ERC配置路径: Project > Project Options > Error Reporting

关键检查项包括:

- Unconnected Pin:未连接的引脚

- Floating Input Pin:悬空输入

- Multiple Drivers on Net:同一网络多个输出驱动

- Power Pin not Driven:电源引脚未供电

例如,若忘记给运放的V+引脚接电源,ERC会报:

“Warning: Power input is not connected (U1: VCC)”

此时需添加Power Port或Net Label予以修正。

3.3.2 网络表生成与跨域一致性分析

网络表(Netlist)是原理图与PCB之间的桥梁。可通过 Design > Update PCB Document 生成差异比较,确保所有元件和网络同步。

建议启用 Compare Pins and Packagings 选项,防止封装引脚不匹配。

3.3.3 常见原理图错误案例解析与修正

| 错误类型 | 典型表现 | 解决方案 |

|---|---|---|

| 悬空输入 | 微控制器GPIO未上拉 | 添加Pull-up电阻或配置内部上拉 |

| 反向电源连接 | 二极管极性接反 | 检查Symbol Pin Direction |

| 网络标签拼写错误 | 3V3 vs 3V3 (含空格) |

使用Find Similar Objects定位 |

| 多重驱动冲突 | 两个Buffer输出接同一Net | 插入Buffer或改用Open-Collector |

通过系统化排查,可大幅降低后期调试成本。

4. 元件库创建与封装管理

在现代电子设计自动化(EDA)流程中,元件库的规范性、完整性与可维护性直接决定了项目开发效率与后期生产的可靠性。Altium Designer作为业界领先的PCB设计平台,其强大的库管理系统不仅支持高度自定义的符号与封装构建,还提供了集成化、结构化的数据管理机制。尤其在复杂系统级设计中,良好的元件库体系能够显著降低出错概率、提升团队协作效率,并为后续生产制造提供准确的数据支撑。

随着电子产品向小型化、高密度、多引脚方向发展,传统的标准库已难以满足实际需求。许多新型器件如QFN、BGA、LGA等封装形式对焊盘尺寸、间距、热过孔布局等提出了严格要求;同时,越来越多的设计采用模块复用和跨项目共享策略,使得建立统一、标准化的内部元件库成为企业级设计流程中的关键环节。因此,深入掌握Altium Designer中元件库的创建逻辑、分类结构以及封装映射机制,是每一位资深硬件工程师必须具备的核心能力。

本章将从底层架构出发,系统剖析Altium Designer中元件库的组织方式,涵盖原理图符号库(SchLib)、PCB封装库(PcbLib)、3D模型嵌入及最终集成库(IntLib)的构建全过程。重点讲解如何通过规范化流程实现符号与封装的精确绑定,解决常见兼容性问题,并引入UUID机制保障元件唯一性,避免版本混乱。此外,还将结合典型应用场景展示多部件IC的设计方法与第三方库的安全导入策略,确保读者能够在真实项目中独立完成高质量元件建模任务。

4.1 元件库体系结构与分类管理

Altium Designer中的元件库并非单一文件,而是一套分层、协同工作的数据库系统。理解其内在结构对于构建可维护、可扩展的设计环境至关重要。整个库体系主要包括三类核心组件: 原理图符号库(*.SchLib) 、 PCB封装库(*.PcbLib) 和 集成库(*.IntLib) ,它们之间通过唯一的标识符(如Designator、Footprint Name、UUID)进行关联,形成完整的元器件信息链。

4.1.1 原理图符号库与PCB封装库的关系

在传统设计流程中,原理图符号仅代表电气连接关系,而PCB封装则描述物理布局特征。两者看似独立,实则通过“封装映射”实现一一对应。例如,一个名为 LM358 的运算放大器,在原理图中可能表现为两个独立的运放单元(U1A、U1B),每个单元具有若干引脚;而在PCB端,则需匹配一个具体的SO-8封装,包含8个焊盘及其精确坐标位置。

这种分离式设计带来了极大的灵活性——同一个符号可以绑定多个不同封装(如DIP-8、SOIC-8、TSSOP-8),便于根据应用场景切换;反之,同一封装也可被多个不同功能器件共用(如多种MCU使用LQFP-64)。但这也增加了管理复杂度,若未建立清晰的映射规则,极易导致网络表错误或布线失败。

为了实现精准关联,Altium Designer引入了“Footprint”属性字段。该字段位于元件属性对话框中,允许用户手动指定或批量导入对应的PCB封装名称。系统在编译项目时会自动检查该引用是否存在,若缺失则触发ERC警告。

| 属性项 | 说明 |

|---|---|

Design Item ID |

元件唯一标识符,用于跨库识别 |

Comment |

器件型号显示文本(常用于BOM输出) |

Description |

功能描述信息 |

Footprint |

指向PcbLib中的具体封装名(如 SOIC-8_3.9x4.9mm_P1.27mm ) |

Manufacturer Part Number |

可选,用于ERP/MES系统对接 |

下面是一个典型的符号-封装映射配置示例:

Component: LM358N (Dual Op-Amp)

- Symbol: LM358.SchLib

- Pin Count: 8

- Parts in Package: 2 (U1A, U1B)

- Footprint: SOIC-8_3.9x4.9mm_P1.27mm [PcbLib: TI_SmallOutline.IntLib]

- UUID: {8A3C2E1D-5F6B-4C9E-A1D2-0F3E4D5C6B7A}

逻辑分析 :上述配置表明,该元件在原理图中使用

LM358.SchLib提供的图形符号,但在PCB布局阶段将调用名为SOIC-8_...的封装。此过程依赖于库路径的正确设置与封装名称的完全匹配。任何拼写差异都会导致“Unresolved Footprint”错误。

此外,Altium支持在同一元件上定义多个封装变体(Alternate Footprints),适用于支持多种安装方式的器件。例如,某电容可同时拥有 0805 贴片封装和 RADIAL 通孔封装,设计师可在原理图放置时选择合适版本。

4.1.2 集成库(Integrated Library)构建流程

集成库( .IntLib )是Altium Designer中最具工程价值的库类型之一。它将多个源库(SchLib + PcbLib + 3D Model)编译为一个不可编辑的二进制文件,具有以下优势:

- 安全性高 :防止误修改原始设计;

- 便于分发 :团队成员只需加载一个文件即可获得完整元件集;

- 加载速度快 :相比加载多个分散库,性能更优;

- 版本控制友好 :适合纳入Git/SVN等版本管理系统。

构建集成库的标准流程如下:

graph TD

A[创建 SchLib 文件] --> B[绘制原理图符号]

B --> C[创建 PcbLib 文件]

C --> D[绘制对应封装]

D --> E[添加 3D STEP 模型(可选)]

E --> F[建立 Symbol-Footprint 映射]

F --> G[新建 Integrated Library 工程 (*.LibPkg)]

G --> H[添加 SchLib 和 PcbLib 到 LibPkg]

H --> I[编译生成 *.IntLib]

I --> J[验证输出结果]

实操步骤详解:

-

新建LibPkg工程

- 菜单栏:File → New → Project → Integrated Library

- 系统自动生成.LibPkg项目文件,并预置空的SchLib和PcbLib模板。 -

导入或创建符号与封装

- 若已有现成库,右键LibPkg →Add Existing to Project;

- 若需新建,右键项目 →Add New to Project → Schematic Library/PCB Library。 -

建立映射关系

- 打开SchLib中目标元件属性;

- 在Models区域点击Add→Footprint;

- 选择对应PcbLib中的封装,或输入名称手动绑定。 -

编译生成IntLib

- 右键LibPkg →Compile Integrated Library

- 成功后生成同名.IntLib文件,默认存放于输出目录(Project Outputs for …) -

验证与安装

- 双击.IntLib文件可在Altium中临时加载;

- 或通过Library Panel → Install → Install from File永久注册。

// 示例代码:Delphi脚本片段(用于自动化库生成)

procedure CreateIntegratedLibrary;

var

LibPkg : ILibraryPackage;

SchLib : ISchematicDocument;

PcbLib : IPCBLibrary;

begin

LibPkg := CreateLibraryPackage;

LibPkg.Name := 'MyCompany.Components.LibPkg';

SchLib := CreateSchematicLibrary;

SchLib.FileName := 'Discrete.SchLib';

LibPkg.AddDocument(SchLib);

PcbLib := CreatePCBLibrary;

PcbLib.FileName := 'Package_SO.PcbLib';

LibPkg.AddDocument(PcbLib);

LibPkg.Compile; // 触发编译动作

end;

参数说明与逻辑分析 :

-CreateLibraryPackage:初始化一个新的集成库容器;

-AddDocument:将源库文档加入编译队列;

-Compile:执行真正的合并与校验操作,生成.IntLib;

- 此脚本可用于批量化生成企业标准库,配合CI/CD流水线实现自动化发布。

值得注意的是,一旦 .IntLib 生成,原始 .SchLib 和 .PcbLib 仍需保留备份,因为 .IntLib 本身无法反向编辑。建议将源库存放在受控服务器(如Altium Vault或Git仓库),并制定明确的更新审批流程。

4.1.3 第三方库导入与兼容性处理

在实际工作中,工程师常常需要使用厂商提供的第三方库(如Texas Instruments、Analog Devices发布的官方库包)。这些库通常以 .Zip 压缩包形式提供,内含 .SchLib 、 .PcbLib 甚至 .IntLib 文件。虽然方便快捷,但也存在诸多兼容性风险。

常见的问题包括:

- 封装尺寸不符合IPC标准;

- 引脚编号与主流命名习惯不符;

- 缺少3D模型或STEP文件精度不足;

- 使用非标准图层(如将丝印画在Top Overlay以外);

- 库文件基于旧版AD格式,导致新版软件解析异常。

为此,应遵循以下安全导入流程:

| 步骤 | 操作内容 | 注意事项 |

|---|---|---|

| 1 | 解压第三方库包 | 查看Readme确认适用AD版本 |

| 2 | 在Altium中打开SchLib/PcbLib | 观察是否有报错提示 |

| 3 | 检查封装焊盘参数 | 对比IPC-7351标准,修正Size/Shape/Tolerance |

| 4 | 核对引脚电气类型 | 如Input/Output/OpenCollector等是否正确 |

| 5 | 添加3D模型(如有) | 推荐使用原厂STEP文件 |

| 6 | 重新建立Symbol-Footprint链接 | 防止路径丢失 |

| 7 | 编译为本地IntLib | 统一纳入公司库管理体系 |

特别提醒:切勿直接将第三方库加入搜索路径长期使用。最佳实践是将其作为“参考源”,经审查后再迁移至内部标准库中,确保所有元件符合企业设计规范。

此外,Altium官方提供的“Managed Content”服务(如Altium Universe)也集成了大量经过认证的器件模型,可通过云订阅方式安全接入,极大降低了库维护成本。

综上所述,元件库的体系化管理不仅是技术问题,更是工程管理的重要组成部分。只有建立起标准化、可追溯、易维护的库结构,才能真正支撑起高效可靠的硬件开发流程。

5. PCB布局与自动/手动布线实战

在现代电子设计中,PCB(Printed Circuit Board)不仅是电路的物理载体,更是决定系统性能、信号完整性与电磁兼容性的关键环节。当原理图设计完成并通过电气规则检查后,真正的挑战才刚刚开始——如何将二维的逻辑连接转化为三维空间中的高效物理实现。本章聚焦于从原理图到PCB版图的转换过程,深入探讨 布局策略、布线机制、自动与手动布线协同优化 等核心实践内容。通过结合Altium Designer强大的交互式环境与工程经验积累,帮助设计师在复杂项目中实现高密度、低噪声、高可靠性的电路板设计。

无论是消费类电子产品的小型化需求,还是工业控制设备对稳定性的严苛要求,合理的布局和精确的布线都是不可或缺的技术基石。尤其是在高频、高速数字或混合信号系统中,元件摆放的位置、走线长度匹配、回流路径规划等因素直接影响系统的整体表现。因此,掌握从初始布局到最终布线全过程的实战技巧,是每一位高级硬件工程师必须具备的核心能力。

5.1 PCB布局策略与物理约束管理

良好的PCB布局是成功设计的第一步。它不仅决定了后续布线的可行性,还影响着散热性能、EMI抑制以及制造成本。一个经过深思熟虑的布局方案能够显著降低后期修改频率,提升一次成功率。

5.1.1 布局基本原则与模块化分区

PCB布局应遵循“功能模块先行”的设计哲学。通常将整个电路划分为若干子系统,如电源管理单元、微控制器核心、模拟前端、通信接口等,并依据其电气特性进行区域划分。

| 模块类型 | 特性描述 | 布局建议 |

|---|---|---|

| 数字逻辑电路 | 高频开关、大电流瞬变 | 靠近电源输入端,远离敏感模拟区 |

| 模拟信号链路 | 微弱信号、易受干扰 | 单独隔离,底层铺地屏蔽 |

| 电源转换模块 | 发热量大、噪声强 | 放置在边缘通风处,避免遮挡其他元件 |

| 射频/高速信号路径 | 对走线长度与时序敏感 | 缩短引脚间距离,保持参考平面完整 |

注意 :不同功能模块之间应设置明确的“护城河”(Keep-Out Zone),防止噪声耦合。

+-----------------------------+

| Digital MCU Core |

| |

+--------+--------------------+

|

v

+--------v--------------------+ +---------------------+

| Power Supply Section |<--->| RF / High-Speed |

+-----------------------------+ +---------------------+

^

|

+--------+--------------------+

| Analog Signal Chain |

| (ADC, Op-Amps, Sensors) |

+-----------------------------+

mermaid流程图如下所示:

graph TD

A[Start Layout] --> B{Identify Functional Blocks}

B --> C[Place Critical Components First]

C --> D[Define Keep-Out Zones]

D --> E[Optimize Signal Flow Path]

E --> F[Thermal Consideration & Airflow]

F --> G[Finalize Mechanical Constraints]

G --> H[Proceed to Routing Phase]

该流程强调了从抽象模块识别到具体物理实现的递进式思考方式,确保每一步都有据可依。

元件优先级排序

在实际操作中,并非所有元件都具有同等重要性。以下是一些常见的优先放置顺序:

- 连接器与接口器件 :作为外部信号进出的门户,位置往往由机械结构限定。

- 主控芯片(MCU/FPGA) :作为系统的“大脑”,应居于中心或便于布线的区域。

- 电源芯片(DC-DC、LDO) 及其周边滤波电容:需靠近负载并形成紧凑回路。

- 晶振与时钟缓冲器 :必须紧邻目标IC,且下方禁止走线以减少寄生效应。

- 去耦电容 :尽可能贴近电源引脚,采用最短路径连接。

这些原则看似简单,但在高密度设计中极易被忽视。例如,若将BGA封装的FPGA置于角落,可能导致外围走线被迫绕行多层,增加阻抗不连续风险。

5.1.2 Altium Designer中的布局工具与交互机制

Altium Designer提供了丰富的布局辅助功能,极大提升了设计效率与准确性。以下是几个关键工具的实际应用方法:

推挤式移动(Push and Shove)

启用 Interactive Routing 模式下的推挤功能后,移动元件时周围的铜箔和走线会自动避让,避免人为造成短路或违反间距规则。

Tools → Preferences → PCB Editor → Interactive Routing

→ 启用 "Allow Push Obstacles"

此功能依赖于实时DRC检测,在移动过程中动态评估是否满足最小间距要求。参数说明如下:

- Push Strength :控制障碍物被推开的力度,默认值为50%,过高可能导致走线变形。

- Hug Tracks :允许新走线贴合已有线路走向,增强一致性。

- Avoid Blocking :防止完全封锁某条关键信号路径。

对齐与分布命令

使用快捷键 A 调出对齐菜单,可快速完成多个元件的整齐排列。常用组合包括:

A → L:左对齐A → C:居中对齐A → T:顶对齐A → S → H:水平均匀分布

这些命令特别适用于DDR内存颗粒、排阻阵列等需要严格对称布局的场景。

网络高亮与飞线引导

按 Ctrl + 左键点击网络名 可高亮显示特定网络的所有连接点及飞线(Ratsnest)。这对于判断关键信号路径是否合理非常有帮助。

例如,在布局阶段就观察到CLK信号跨越了整个板子,提示可能需要重新调整驱动源位置,以缩短传输距离。

flowchart LR

subgraph Before_Optimization

direction LR

CLK_Source -->|Long Trace| Load_IC

end

subgraph After_Optimization

direction LR

CLK_Source -->|Short Direct Route| Load_IC

end

Before_Optimization -- Reduce Length --> After_Optimization

上述流程图展示了通过优化布局缩短时钟信号路径的过程,体现了早期干预的重要性。

5.1.3 机械约束与禁布区设置

在真实产品中,PCB常需适配外壳、散热片、螺丝柱或其他内部组件。此时必须定义清晰的机械边界与禁止布线区域。

创建Keep-Out Layer

- 切换至

Keep-Out Layer - 使用

Place → Line或Rectangle绘制封闭区域 - 设置属性为“禁止布线”或“禁止放置元件”

Layer: Keep-Out Layer

Object Type: Track/Arc/Fill

Rule Scope: All Layers or Specific Layer(s)

该区域将在所有允许的层上生效,阻止任何电气对象进入。

定义Room(房间)

对于某些专用模块(如电源模块),可以创建Room来限定其内部元件只能在此范围内布局。

Design → Rooms → Place Rectangular Room

右键Room → Properties 可指定:

- 所属网络类(Net Class)

- 默认布线层

- 是否锁定位置

一旦设定,未分配至该Room的元件无法放入其中,有助于维护设计秩序。

5.1.4 热管理与气流导向设计

高功耗元件(如MOSFET、PMIC)会产生大量热量,若不妥善处理,会导致局部温升超标,影响寿命甚至引发故障。

散热焊盘(Thermal Pad)处理

许多QFN或PowerSO封装底部带有裸露金属垫,必须通过多个小孔连接到底层大面积铺铜,以增强导热能力。

Pad Properties:

Shape: Rectangle

Layer: Multi-Layer

Plated: Yes

Thermal Relief: Spoke Width = 0.3mm, Gap = 0.2mm

热释放(Thermal Relief)设计防止因过快散热导致焊接困难,同时保证足够的热传导效率。

敷铜与散热过孔阵列

使用 Polygon Pour 功能在底层或内层铺设大面积GND铜皮,并围绕发热元件布置8~12个直径0.3mm的过孔阵列,形成“热烟囱”效应。

graph BT

Heat_Source --> Thermal_Pad

Thermal_Pad --> Via_Array[Via Array x10]

Via_Array --> Bottom_Copper[Bottom Layer Copper Pour]

Bottom_Copper --> Heatsink_or_Airflow

这种结构能有效将热量传递至外层或机箱,提升整体散热性能。

5.1.5 布局复查清单(Layout Checklist)

为确保无遗漏,建议在进入布线前执行以下核查:

- ✅ 所有关键元件已按优先级放置完毕

- ✅ 高速/时钟信号路径最短化

- ✅ 模拟与数字区域分离并加地隔离

- ✅ 电源模块靠近输入端且有足够散热空间

- ✅ 所有去耦电容贴近电源引脚

- ✅ 连接器方向与外壳匹配,无干涉

此清单可作为团队协作的标准文档,提高交付质量的一致性。

5.2 自动布线与手动布线的协同优化

尽管自动布线技术发展多年,但在复杂设计中仍难以完全替代人工干预。理想的做法是利用自动布线完成基础连接,再通过手动布线进行关键路径优化。

5.2.1 自动布线引擎的选择与配置

Altium Designer内置两种主要布线器:

- Situs Topological Autorouter :基于拓扑分析,适合高密度复杂板

- External Autorouters (如FastRoute):支持更高级算法,但需额外授权

推荐使用Situs进行初步布线:

Route → Auto Route → All

在弹出对话框中设置:

| 参数 | 推荐值 | 说明 |

|---|---|---|

| Routing Layer Usage | Top & Bottom | 指定可用层 |

| Net Preference | Power > Clock > Signal | 优先处理关键网络 |

| Routing Grid | 5mil 或 2.5mil | 匹配设计精度 |

| Via Style | Blind/Buried (if applicable) | 控制过孔类型 |

执行后生成的布线结果需进一步审查,尤其是拐角数量、过孔数目和长度匹配情况。

5.2.2 关键信号的手动布线实践

对于时钟、差分对、DDR数据线等高速网络,必须采用手动布线以确保信号完整性。

差分对布线示例(USB D+/D-)

Net: USB_DP, USB_DM

Rules: Differential Pairs Routing

操作步骤:

- 在

Design → Classes → Differential Pair Classes中添加差分对 - 设置差分阻抗为90Ω±10%

- 使用

Interactive Diff Pair Routing工具(快捷键T → R → D) - 保持等长、等距,避免锐角转弯

// 示例:差分对布线参数设置(通过规则编辑器)

Rule Name: USB_DiffPair

Rule Scope: Match Net Names 'USB_DP' and 'USB_DM'

Constraints:

- Minimum Width: 0.2mm

- Preferred Width: 0.25mm

- Maximum Gap: 0.15mm

- Target Impedance: 90 Ohm

- Length Tuning: ±50mil

逐行解析:

Rule Name: 自定义规则名称,便于识别;Rule Scope: 定义适用对象,此处为特定网络名匹配;Minimum/Preferred Width: 控制线宽范围,影响阻抗;Maximum Gap: 限制两条线之间的最大间距,维持差模特性;Target Impedance: 设定目标差分阻抗,AD据此计算线宽;Length Tuning: 允许的长度偏差,用于后期调谐。

此类精细化控制是保障USB通信稳定的基础。

5.2.3 布线后的优化与重布线策略

即使已完成布线,仍可通过以下手段持续优化:

- 泪滴补强(Teardrops) :在焊盘与走线交接处添加渐变过渡,增强机械强度

- 覆铜修整(Polygon Pour Modify) :刷新敷铜以反映最新布线变化

- 蛇形走线(Meander) :用于长度匹配,如DDR地址线

sequenceDiagram

participant Designer

participant AD as Altium Designer

Designer->>AD: Run Auto Router

AD-->>Designer: Generate Initial Routes

Designer->>AD: Identify Critical Nets

AD-->>Designer: Highlight DRC Violations

Designer->>AD: Manual Tune High-Speed Paths

AD-->>Designer: Revalidate with SI Tool

Designer->>AD: Finalize & Archive

该序列图描绘了自动化与人工干预交替进行的设计闭环,体现现代PCB开发的真实工作流。

综上所述,PCB布局与布线并非孤立步骤,而是相互制约、反复迭代的过程。唯有深入理解工具能力与物理规律,方能在有限空间内创造出高性能、高可靠的产品。

6. 多层板层叠结构与过孔设计

在现代高速、高密度电子系统中,单双面板已无法满足日益复杂的布线需求。随着信号完整性、电源完整性和电磁兼容性要求的不断提升,多层印刷电路板(PCB)成为主流解决方案。多层板通过引入多个信号层、电源层和地层,不仅显著提升了布线空间利用率,还为阻抗控制、串扰抑制、回流路径优化等关键性能提供了物理基础。其中, 层叠结构设计 与 过孔策略规划 是决定多层板电气性能与制造可行性的两大核心环节。

合理的层叠结构能够有效降低噪声耦合、提升散热能力,并为差分对提供稳定的参考平面;而科学的过孔使用方式则直接影响信号完整性、电源分配网络(PDN)效率以及整体可靠性。尤其在GHz级高速数字或射频应用中,盲孔、埋孔和微孔的选择甚至会成为制约产品性能的关键因素。因此,深入理解层叠设计原则与过孔工作机制,对于实现高性能、低成本、可量产的PCB至关重要。

本章将从层叠结构的基本构成出发,逐步剖析其设计逻辑与工程权衡,并结合实际案例探讨不同应用场景下的最优配置方案。同时,围绕通孔、盲孔、埋孔及微孔的技术特性展开分析,揭示其在信号传输中的寄生效应及其对高频响应的影响机制。最终通过Altium Designer中的具体操作流程,展示如何在EDA环境中精确建模并验证多层结构与过孔参数。

6.1 多层板层叠结构的设计原理与工程实践

多层板的层叠结构是指PCB中各导电层(信号层、电源层、地层)与介质层(Prepreg和Core)在垂直方向上的排列组合方式。这一结构不仅决定了板材的机械厚度与热膨胀系数,更深刻影响着信号传播速度、特征阻抗、串扰水平和EMI辐射特性。一个精心设计的层叠方案能够在不增加额外成本的前提下,大幅提升系统的电气性能。

6.1.1 层叠结构的核心组成要素

一个多层PCB通常由以下几个基本单元构成:

| 组成部分 | 功能说明 |

|---|---|

| Signal Layer(信号层) | 用于走线传输数据、时钟或其他模拟/数字信号 |

| Power Plane(电源层) | 提供稳定电压供给,降低电源噪声,增强去耦效果 |

| Ground Plane(地层) | 构建低阻抗回流路径,屏蔽干扰,提升信号完整性 |

| Dielectric Layer(介质层) | 分隔相邻导电层,决定层间电容与介电常数 |

| Prepreg(半固化片) | 粘结Core与铜箔,在压合过程中流动填充间隙 |

| Core(芯板) | 带有铜箔的刚性基材,作为内部结构支撑 |

这些材料在高温高压下经过层压工艺形成一体化结构。例如,一个典型的六层板可能采用如下堆叠顺序(自上而下):

Top Signal Layer

Prepreg

Internal Power Plane (Layer 2)

Core

Internal Ground Plane (Layer 3)

Prepreg

Bottom Signal Layer

这种“对称分布”结构有助于减少翘曲变形,提高 manufacturability(可制造性)。Altium Designer 支持在 PCB Stackup Manager 中直观定义此类结构。

mermaid

graph TD

A[顶层信号层] --> B[PP介质]

B --> C[内电层 Layer2]

C --> D[Core基板]

D --> E[内地层 Layer3]

E --> F[PP介质]

F --> G[底层信号层]

style A fill:#e6f7ff,stroke:#333

style G fill:#ffe6e6,stroke:#333

style C fill:#fff2cc,stroke:#333

style E fill:#d9ead3,stroke:#333

该流程图展示了六层板典型对称层叠结构的垂直堆叠关系,强调了介质层与导电层之间的交替排布逻辑。

6.1.2 层叠设计的关键考量因素

设计层叠结构时需综合考虑以下五个维度:

- 层数选择 :根据功能复杂度确定总层数。四层板适用于一般嵌入式系统;六至八层常见于FPGA、处理器主板;十层以上多见于通信设备或高端服务器。

- 参考平面连续性 :确保高速信号下方存在完整地或电源平面,避免跨分割导致回流路径断裂。

- 阻抗控制精度 :利用工具计算微带线或带状线的特征阻抗(如50Ω单端、100Ω差分),并通过调整介质厚度与线宽实现匹配。

- 电源完整性支持 :增加专门的电源/地平面对以构建低感抗PDN,配合去耦电容形成高效滤波网络。

- 制造成本与周期 :更多层数意味着更高原材料成本与更长交期,应避免过度设计。

以一款基于ARM Cortex-A72的应用处理器模块为例,其接口包括DDR4内存、PCIe Gen3、USB 3.0和千兆以太网,均属高速信号范畴。此时推荐采用8层板设计,典型层叠如下表所示:

| 层号 | 名称 | 类型 | 厚度 (mil) | 材料 |

|---|---|---|---|---|

| L1 | Top Signal | 信号层 | 1.4 | Copper |

| L2 | Internal GND | 地层 | 1.4 | Copper |

| L3 | Internal Signal1 | 信号层 | 1.4 | Copper |

| L4 | Internal Power1 | 电源层 | 1.4 | Copper |

| L5 | Internal Power2 | 电源层 | 1.4 | Copper |

| L6 | Internal Signal2 | 信号层 | 1.4 | Copper |

| L7 | Internal GND | 地层 | 1.4 | Copper |

| L8 | Bottom Signal | 信号层 | 1.4 | Copper |

介质配置建议:

- L1-L2: 4mil Prepreg (FR-4, εr=4.2)

- L2-L3: 10mil Core

- L3-L4: 4mil Prepreg

- L4-L5: 20mil Core(主电源区域)

- L5-L6: 4mil Prepreg

- L6-L7: 10mil Core

- L7-L8: 4mil Prepreg

此结构实现了两个完整的地层包围中间信号层,极大减少了串扰风险,同时也为DDR4布线提供了理想的参考平面。

6.1.3 在Altium Designer中配置层叠结构

Altium Designer 提供了强大的 Layer Stack Manager 工具,允许用户精确设定每层的物理属性与电气参数。以下是具体操作步骤:

- 打开PCB文件后,点击菜单栏

Design → Layer Stack Manager。 - 在弹出窗口中,默认显示双层结构。点击左侧“Add Layer”按钮添加内部信号或平面层。

- 双击每一层可修改其类型、名称、厚度、铜厚、介电常数(εr)及损耗角正切(Df)。

- 设置完毕后点击“Apply”保存,系统自动更新所有相关规则(如阻抗计算)。

// 示例:Altium脚本片段(Delphi Script),用于批量创建标准8层堆叠

procedure CreateStandard8LayerStack;

var

Stack : TLayerStack;

begin

Stack := PCB.LayerStack;

Stack.Clear;

// 添加L1 (Top Layer)

Stack.AddSignalLayer(clTop, 'Top Signal', 1.4);

// 添加L2 (GND Plane)

Stack.AddPlaneLayer(clInternal2, 'Internal GND', 1.4);

// 插入介质:4mil prepreg

Stack.AddDielectricLayer('PP_L1L2', 4.0, 4.2, 0.02);

// 继续添加其余层...

end;

代码逻辑逐行解读 :

- 第3行:获取当前PCB文档的层堆栈对象;

- 第4行:清空现有堆叠配置,防止冲突;

- 第7行:使用AddSignalLayer方法添加顶层信号层,参数分别为层ID、名称和铜厚(单位为mil);

- 第10行:添加内部地层;

- 第13行:调用AddDielectricLayer插入非导电介质层,参数依次为名称、厚度、相对介电常数和损耗因子;

- 后续可通过循环结构自动化生成完整堆叠。

该脚本可用于企业级模板标准化部署,提升团队协作效率。

此外,Altium 支持与 Polar SI9000 阻抗计算器集成,可在Layer Stack Manager中直接调用外部引擎进行精确阻抗建模。例如,当设计USB 3.0差分对时,可设定目标阻抗为90Ω±10%,然后调整走线宽度直至满足要求。

综上所述,层叠结构并非简单的“层数越多越好”,而是需要基于系统需求、信号速率、功耗分布和预算限制进行系统化权衡。只有将理论知识与EDA工具能力深度融合,才能真正发挥多层板的技术优势。

6.2 过孔设计类型与高频信号影响分析

过孔(Via)是连接不同PCB层之间导电路径的关键结构,其实质是一个镀铜通孔,贯穿一层或多层介质材料。尽管看似简单,但过孔在高速电路中扮演着远超“电气连接点”的角色——它引入了不可忽视的寄生电感与电容,改变了信号的传播特性,甚至可能引发反射、振铃和模式转换等问题。

6.2.1 过孔的主要分类与结构差异

根据连通范围的不同,过孔可分为以下几类:

| 类型 | 定义 | 适用场景 | 制造难度 |

|---|---|---|---|

| Through-Hole Via(通孔) | 贯穿整个PCB的所有层 | 普通低速板、原型验证 | ★☆☆☆☆(最低) |

| Blind Via(盲孔) | 连接外层与一个或多个内层,不穿透整板 | 高密度HDI板、BGA封装逃逸 | ★★★★☆ |

| Buried Via(埋孔) | 仅连接内部层,两端均不在表面 | 超高密度互连设计 | ★★★★★ |

| Microvia(微孔) | 直径≤0.15mm,通常激光钻孔制成 | 移动终端、FPGA扇出区 | ★★★★☆ |

其中,微孔又可根据加工方式分为:

- Type I : 表层到第一内层(L1→L2)

- Type II : 内层间连接(L2↔L3)

- Stacked Microvias : 多个微孔垂直堆叠

- Staggered Microvias : 错位排列以提升可靠性

mermaid

flowchart TB

A[Via Types] --> B[Through-Hole]

A --> C[Blind Via]

A --> D[Buried Via]

A --> E[Microvia]

E --> E1[Laser Drilled]

E --> E2[Diameter ≤ 0.15mm]

E --> E3[Used in HDI]

style B fill:#cce5ff

style C fill:#d4edda

style D fill:#f8d7da

style E fill:#fff3cd

该流程图清晰划分了各类过孔的层级关系,突出其技术演进路径与应用场景差异。

6.2.2 过孔的电气模型与寄生参数提取

在高频(>500MHz)环境下,过孔不能再被视为理想短路,而应建模为分布RLC网络。典型的小信号等效电路如下:

C_pad_top

|

L_via --- C_via_annular

|

C_pad_bottom

其中:

- L_via :过孔壁的寄生电感,约为1~2nH/mm长度;

- C_via :过孔焊盘与周围平面间的寄生电容,典型值0.1~0.3pF;

- C_pad :顶层与底层焊盘对地电容;

- R :镀层电阻,通常忽略。

假设一个通孔总长2mm,直径0.3mm,焊盘直径0.6mm,间距1mm,则可用经验公式估算:

L_{via} \approx 5.08h \cdot \ln\left(\frac{4h}{d}\right) \quad [\text{nH}]

C_{via} \approx \frac{1.41\varepsilon_r T D_1 D_2}{(D_2 - D_1)(D_1 + D_2)} \quad [\text{pF}]

代入 $ h=2 $, $ d=0.3 $, $ \varepsilon_r=4.2 $, $ D_1=0.6 $, $ D_2=1.0 $ 得:

- $ L_{via} ≈ 10.2 \, \text{nH} $

- $ C_{via} ≈ 0.25 \, \text{pF} $

由此可得谐振频率:

f_r = \frac{1}{2\pi\sqrt{LC}} ≈ 3.16 \, \text{GHz}

这意味着该过孔在3GHz附近会发生并联谐振,导致阻抗突增,严重劣化信号质量。

6.2.3 Altium Designer中的过孔管理与规则设置

在Altium中,可通过 Via Style Routing 和 Design Rule 实现精细化控制。例如,设定不同网络使用不同类型过孔:

Rule Name: HighSpeed_Via_Control

Scope: Net in ('DDR_DQ*', 'PCIe_*')

Constraints:

- Minimum Hole Size = 0.2mm

- Maximum Hole Size = 0.3mm

- Allowed Via Types = Microvia, Blind/Buried

- Prefer Smallest Via

此外,在交互式布线时启用 Auto-Match Layers 功能,可让软件自动选择合适的过孔类型完成层切换。

// 示例:PCB via定义语句(文本格式导出)

ViaDefinition V1

{

Diameter = 0.6 mm

HoleSize = 0.3 mm

TopToBottom = Yes

BlindOrBuriedMode = None

StartLayer = Top Layer

StopLayer = Bottom Layer

}

参数说明 :

-Diameter: 过孔外径;

-HoleSize: 钻孔直径;

-TopToBottom: 是否为通孔;

-BlindOrBuriedMode: 控制盲埋孔行为;

-Start/StopLayer: 明确起止层。

结合高速规则检查器(High Speed Design Rule Checker),可在编译阶段检测是否存在“禁止使用的过孔类型”,从而提前规避潜在风险。

综上,过孔不仅是物理连接手段,更是影响信号完整性的关键元件。合理选择类型、优化布局位置、控制数量密度,已成为高速PCB设计不可或缺的一环。

7. 设计规则与约束设置(电气、间距、布线)

7.1 设计规则系统概述与优先级机制

Altium Designer 的设计规则系统是整个 PCB 设计流程的核心保障,它不仅确保电路在物理实现上的可行性,还直接影响产品的可靠性与电磁兼容性(EMC)。设计规则(Design Rules)贯穿从布局到布线、从电气特性到制造工艺的各个环节。这些规则在 PCB 编辑器 中通过 “设计” → “规则”(Design → Rules) 打开,进入 PCB Rules and Constraints Editor 界面。

该编辑器采用树状分类结构,包含以下主要类别:

| 规则类别 | 功能说明 |

|---|---|

| Electrical | 电气连接性检查,如短路、开路等 |

| Routing | 布线宽度、层数、拓扑结构等控制 |

| SMT | 表面贴装元件焊盘相关规则 |

| Mask | 阻焊层和锡膏层扩展设置 |

| Plane | 内电层连接方式与分割管理 |

| Testpoint | 测试点生成策略 |

| Manufacturing | 制造相关限制,如最小孔径、线宽等 |

| High Speed | 高速信号匹配、等长、差分对等 |

| Placement | 元件布局间距与区域限制 |

| Signal Integrity | 信号完整性分析参数 |

每条规则具有明确的作用范围(Scope),支持逻辑表达式定义适用对象。例如:

InNet('GND') AND InComponentClass('Power IC')

表示“仅作用于‘Power IC’类组件中的 GND 网络”。

规则优先级由上至下递减,高优先级规则会覆盖低优先级设定。建议将特殊网络(如电源、高速信号)的规则置于顶部,通用规则放底部。

7.2 电气规则与安全间距配置实践

电气规则(Electrical Rules)主要用于防止非法连接,典型包括:

- 未连接引脚检测(Un-Routed Net)

- 短路允许性(Allow Short Circuit)

- 未指定网络(No Net)处理

实际项目中常需禁用某些默认警告。例如,在调试接口中允许多个测试点共享同一网络时,可配置:

Rule Name: Allow_Tests_Short

Scope: InNet('TEST_POINT_BUS')

Allow Short-Circuit: True

安全间距(Clearance)规则 是物理隔离的关键,决定铜皮之间最小空气间隙。设置路径如下:

- 进入

Design → Rules → Electrical → Clearance - 新建规则,命名如

Clr_10mil_Main - 设置作用范围(Full Query):

plaintext (All) AND (Not InNet('HV_PRIMARY')) - 配置净距值为

10mil - 对高压网络单独建立规则:

plaintext Name: Clr_25mil_HV Scope: InNet('HV_PRIMARY') Minimum Clearance: 25mil

可通过 Violation Viewer 实时查看冲突位置,并结合 DRC 报告优化布局。

示例:常见安全间距参考表(FR4 板材,污染度2级)

| 工作电压 (V) | 推荐爬电距离 (mil) | 推荐电气间隙 (mil) |

|---|---|---|

| 5 | 5 | 5 |

| 24 | 8 | 8 |

| 48 | 10 | 10 |

| 120 | 15 | 20 |

| 230 | 25 | 30 |

| 400 | 40 | 50 |

| 690 | 60 | 80 |

| 1000 | 100 | 120 |

| 2500 | 250 | 300 |

| 5000 | 500 | 600 |

注:以上数据依据 IPC-2221 标准估算,实际应结合海拔、涂层等因素修正。

7.3 布线约束与差分对规则高级应用

布线规则(Routing Constraints)直接影响信号质量,尤其在高速数字与射频设计中至关重要。核心参数包括:

- 导线宽度(Width)

- 布线层限制(Routing Layers)

- 拓扑结构(Topology)

- 差分对设置(Differential Pairs)

- 等长控制(Matched Length)

差分对规则配置步骤:

- 定义差分对:

plaintext Tools → Differential Pair Manager → Add Pair Positive: USB_DP, Negative: USB_DM -

创建专属布线规则:

- 名称:Route_USB_Diff

- 范围:InDifferentialPair('USB_DIFF')

- 差分对间距:8mil

- 线宽:10mil

- 允许松耦合模式:启用 -

设置等长规则:

plaintext Category: High Speed → Matched Net Lengths Name: Len_Match_USB Scope: InDifferentialPair('USB_DIFF') Tolerance: ±50mil

布线过程中使用 Interactive Diff Pair Routing 工具(快捷键 Ctrl+Shift+鼠标左键 )可同步推挤两条线路,保持阻抗连续性。

自动布线前的约束准备流程图:

graph TD

A[启动 PCB Rules Editor] --> B{是否已有模板?}

B -- 是 --> C[导入 .rul 文件]

B -- 否 --> D[新建电气规则]

D --> E[设置 Clearance 和 Short-Circuit]

E --> F[定义 Power Net Width]

F --> G[添加 Differential Pair Rules]

G --> H[配置 High-Speed 匹配长度]

H --> I[设定 Manufacturing 最小孔/线]

I --> J[运行 Design Rule Check]

J --> K[修复 Violations]

K --> L[启用自动布线引擎]

此外,可利用 Parameter Management 为网络添加自定义属性,如 Impedance = 90Ω differential ,便于后续 SI 分析调用。

所有规则均可导出为 .rul 文件,用于团队标准化或复用至其他项目,提升协同效率。

简介:Altium Designer是一款广泛应用于电子设计领域的强大PCB设计软件,集成了电路原理图设计、PCB布局、3D查看、信号完整性分析和项目管理等核心功能。本学习资料包内容系统完整,涵盖从基础操作到高级设计的全流程知识,包含教程、示例项目与参考手册,帮助用户掌握元件库管理、原理图绘制、PCB布线规则、仿真分析及制造文件输出等关键技能,适合初学者和进阶用户提升电子设计能力。

openvela 操作系统专为 AIoT 领域量身定制,以轻量化、标准兼容、安全性和高度可扩展性为核心特点。openvela 以其卓越的技术优势,已成为众多物联网设备和 AI 硬件的技术首选,涵盖了智能手表、运动手环、智能音箱、耳机、智能家居设备以及机器人等多个领域。

更多推荐

已为社区贡献34条内容

已为社区贡献34条内容

所有评论(0)