从数字电路到 FPGA 系统设计 一步步搭建属于你的“数字积木”

pwd=open 提取码: open。这本书以 Verilog HDL + Vivado + FPGA工程实践 为主线,从基础逻辑设计一直讲到 CPU、图像处理、DSP等完整系统案例,帮助读者真正理解现代数字系统是如何构建的。但在真实工程环境中,数字系统设计早已发生了巨大的变化——《搭建你的数字积木——数字电路与逻辑设计(Verilog HDL & Vivado版)》正是在这样的背景下诞生的一本教

在很多高校课程体系中,数字电路往往停留在逻辑门、电路化简、卡诺图等传统理论层面。但在真实工程环境中,数字系统设计早已发生了巨大的变化——

今天的逻辑系统设计,已经从:

-

中小规模逻辑芯片

-

手工电路分析

转向:

-

FPGA + 硬件描述语言

-

模块化系统设计

-

复杂数字系统实现

《搭建你的数字积木——数字电路与逻辑设计(Verilog HDL & Vivado版)》正是在这样的背景下诞生的一本教材。

这本书以 Verilog HDL + Vivado + FPGA工程实践 为主线,从基础逻辑设计一直讲到 CPU、图像处理、DSP等完整系统案例,帮助读者真正理解现代数字系统是如何构建的。

一本“工程化”的数字电路教材

与传统数字电路教材不同,本书的核心理念是:

-

用 FPGA 的方式重新理解数字系统设计。

书中强调三个重要思想:

1 模块化设计(Digital Building Blocks)

作者将数字系统比作 “搭积木”:

每个模块都是一个逻辑积木

系统设计就是不断组合这些积木

例如:

-

UART通信模块

-

VGA显示模块

-

RAM控制模块

-

图像采集模块

这些模块不仅讲解原理,还提供 完整设计实例。

2 Verilog + Vivado 真实开发流程

本书直接采用 Xilinx FPGA + Vivado工具链,读者可以从第一章开始就进入真实工程环境:

-

Vivado设计流程

-

Verilog HDL设计

-

IP封装

-

系统集成

-

硬件调试

而不是停留在抽象电路理论。

3 从基础到系统案例

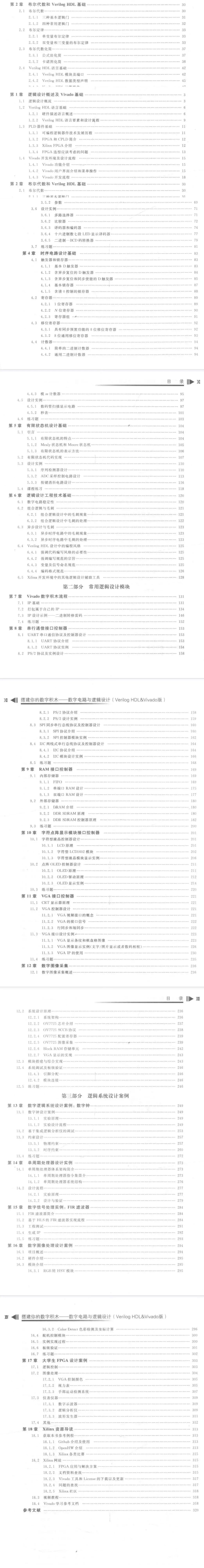

全书共 18章,结构非常清晰:

基础逻辑设计

→ 常用逻辑模块 → 完整数字系统案例

读者可以逐步构建自己的 FPGA 技术体系。

第一部分:逻辑设计基础

这一部分建立数字系统设计的核心基础。

主要内容包括:

Vivado与Verilog入门

FPGA与PLD发展

Verilog HDL基础

Vivado设计流程

让读者快速进入 FPGA设计环境。

组合逻辑设计

书中系统介绍了:

always块

if / case 语句

循环语句

参数化设计

并通过实例讲解:

多路选择器

编码器 / 译码器

七段数码管驱动

BCD转换

时序逻辑设计

包括数字系统最核心的结构:

D触发器

寄存器

移位寄存器

计数器

典型实例:

数码管扫描显示

秒表设计

状态机设计

状态机是 FPGA 设计中最重要的设计方法之一。

书中讲解:

Moore状态机

Mealy状态机

FSM代码结构

设计案例包括:

序列检测器

ADC控制器

按键消抖

工程设计技巧

还专门介绍:

毛刺问题

异步电路

编码风格规范

设计稳定性

这些内容都是 真实工程中经常遇到的问题。

第二部分:常用逻辑模块

这一部分开始进入 工程级模块设计。

IP与模块化设计

首先介绍 Vivado IP流程:

IP封装

IP复用

模块化系统构建

这是大型 FPGA 项目开发的关键技能。

串行通信接口

本书实现了多个经典通信接口:

UART

PS/2

SPI

I2C

这些都是嵌入式系统与 FPGA 中最常见的接口协议。

存储控制器

包括:

FIFO设计

单端口 RAM

双端口 RAM

DDR SDRAM 控制器

这些模块是 高速数据系统的基础。

显示接口设计

书中实现了多种显示系统:

LCD1602字符屏

OLED点阵屏

VGA视频显示

通过这些模块可以实现:

图形界面

数据可视化

简单视频系统

数字图像采集系统

书中还介绍了完整的 摄像头采集系统:

使用 OV7725 CMOS摄像头。

系统包含:

SCCB配置

图像采集

BRAM缓存

VGA显示

读者可以构建一个完整的 FPGA图像采集系统。

第三部分:数字系统设计案例

最后一部分是整本书最精彩的内容——

完整系统级设计案例。

数字钟系统

通过这个案例学习:

模块化系统设计

逻辑分析仪调试

时序约束

单周期CPU

书中实现了一个 单周期处理器:

包括:

指令系统

CPU结构

执行流程

这是理解计算机体系结构的重要实践案例。

FIR数字滤波器

DSP设计案例包括:

FIR滤波器原理

HLS设计流程

IP生成

读者可以理解 FPGA 在 数字信号处理中的应用。

图像处理系统

案例包括:

RGB → HSV颜色空间转换

颜色检测

坐标计算

舵机控制

可以构建一个 简单视觉识别系统。

学生FPGA项目

书中还收录了一些学生创新项目:

例如:

数字示波器

逻辑分析仪

波形发生器

手势识别系统

这些案例展示了 FPGA在仪器与系统设计中的应用潜力。

完整教学资源支持

本书还提供了完整的学习资源:

Github源代码

教学视频

实验操作视频

PPT课件

读者可以:

边学边做

边做边调试

真正掌握 FPGA 系统设计。

总结

它不仅是一本教材,更像一本 FPGA工程实践指南。

如果把数字系统设计比作搭积木,那么:

-

Verilog 是积木语言

-

FPGA 是积木平台

-

模块化设计就是搭建方式

而这本书,正是教你 如何搭建属于自己的数字系统世界。

图书链接

通过网盘分享的文件:搭建你的数字积木 数字电路与逻辑设计(Verilog HDLVivado版) (汤勇明 张圣清) .pdf 链接: https://pan.baidu.com/s/1MbCbw4c1S2kKqPsuIpYJ8A?pwd=open 提取码: open

PS:如果本书对您有帮助,请购买正版书籍。另,本文分享资源只为了学习沟通,切勿商用,商用引起的任何纠纷与本公众号无关~

openvela 操作系统专为 AIoT 领域量身定制,以轻量化、标准兼容、安全性和高度可扩展性为核心特点。openvela 以其卓越的技术优势,已成为众多物联网设备和 AI 硬件的技术首选,涵盖了智能手表、运动手环、智能音箱、耳机、智能家居设备以及机器人等多个领域。

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)