嵌入式网络简介

首先,嵌入式网络硬件分为两部分:MAC 和PHY。如果一款芯片数据手册说自己支持网络,一般都是说的这款SoC 内置MAC,MAC 类似I2C 控制器、SPI 控制器一样的外设。光有MAC还不能直接驱动网络,还需要另外一个芯片:PHY,因此对于内置MAC 的SoC,其外部必须搭配一个PHY 芯片。但是有些SoC 内部没MAC,那也就没法搭配PHY 芯片了,这些内部没有 网络MAC 的芯片如何上网呢?

1、嵌入式网络硬件

首先,嵌入式网络硬件分为两部分:MAC 和PHY。如果一款芯片数据手册说自己支持网络,一般都是说的这款SoC 内置MAC,MAC 类似I2C 控制器、SPI 控制器一样的外设。

光有MAC还不能直接驱动网络,还需要另外一个芯片:PHY,因此对于内置MAC 的SoC,其外部必须搭配一个PHY 芯片。但是有些SoC 内部没MAC,那也就没法搭配PHY 芯片了,这些内部没有 网络MAC 的芯片如何上网呢?这里就要牵扯出常见的两个嵌入式网络硬件方案了。

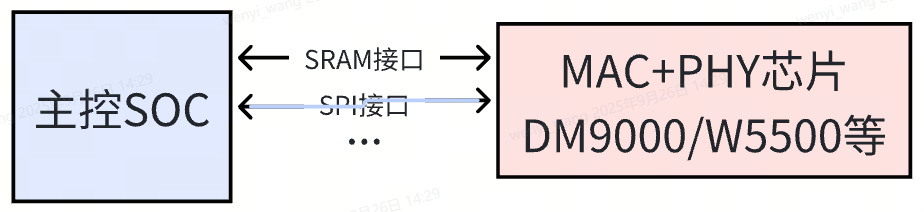

1.1 SOC 内部没有网络MAC 外设

一般这种外置的网络芯片都是MAC+PHY 一体的。比如三星linux 开发板里面用的最多的DM9000,因为三星的芯片基本没有内部MAC(比如S3C2440、S5PV210,4412 等),所以三星的开发板都是通过外置的DM9000 来完成有线网络功能的,DM9000 对SoC 提供了一个SRAM 接口,SOC 会以SRAM 的方式操DM9000。

有些外置的网络芯片更强大,内部甚至集成了硬件TCP/IP 协议栈,对外提供一个SPI 接

口,比如W5500。这个一般用于单片机领域,单片机通过SPI 接口与W5500 进行通信,由于

W5500 内置了硬件TCP/IP 协议栈,因此单片机就不需要移植负责的软件协议栈,直接通过SPI

来操作W5500,简化了单片机联网方案。

这种方案的优点就是让不支持网络的SoC 能够另辟蹊径,实现网络功能,但是缺点就是网

络效率不高,因为一般芯片内置的MAC 会有网络加速引擎,比如网络专用DMA,网络处理效

率会很高。而且此类芯片网速都不快,基本就是10/100M。另外,相比PHY 芯片而言,此类芯

片的成本也比较高,可选择比较少。

SoC 与外部MAC+PHY 芯片的连接如图:

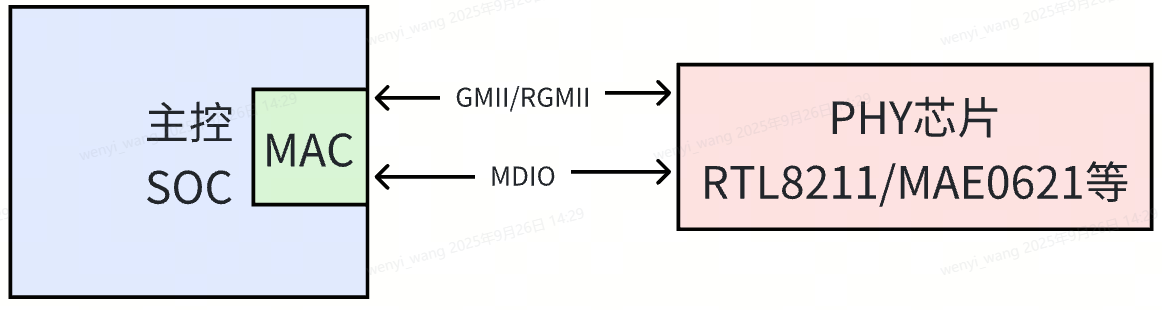

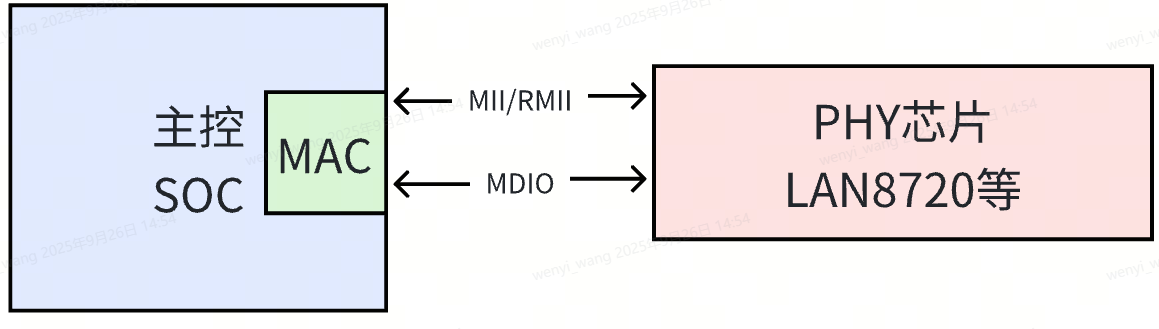

1.2 SOC 内部集成网络MAC 外设

一般说某个SoC 支持网络,就是SoC内部集成网络MAC 外设,此时还需要外接一个网络PHY 芯片。

一般常见的通用SoC 都会集成网络MAC 外设,比如RK 系列、NXP 的I.MX 系列以及STM32MP1 系列,内部集成网络MAC 的优点如下:

①、内部MAC 外设会有专用的加速模块,比如专用的DMA,加速网速数据的处理。

②、网速快,可以支持10/100/1000M 网速。

③、外接PHY 可选择性多,成本低。

内部的MAC 外设会通过相应的接口来连接外部PHY 芯片,根据数据传输模式不同,大致

可以分为以下两类:

①、MII/RMII 接口:支持10Mbit/s 和100Mbit/s 数据传输模式;

②、GMII/RGMII 接口:支持10Mbit/s、100Mbit/s 以及1000Mbit/s 数据传输模式。

从这里可以知道,MII/RMII 接口最大传输速率为100Mbit/s,而GMII/RGMII 接口最大传

输速率可达1000Mbit/s;所以笔者一般把MII/RMII 称为百兆以太网接口,而把GMII/RGMII 称

为千兆以太网接口。

另外主控SoC 需要配置或读取PHY 芯片,也就是读写PHY 的内部寄存器,所以还需要一个控制接口,叫做MIDO,MDIO 很类似IIC,也是两根线,一根数据线叫做MDIO,一根时钟线叫做MDC。

SoC 内部MAC 外设与外部PHY 芯片的连接如图所示:

目前主流千兆PHY主要有Realtek的RTL8211系列,国产的有联芸科技的MAE0621系列,从数据手册及实际分析调试看,MAE0621系列和RTL8211完全PIN to PIN兼容,软件上相关配置和功能也基本一致(如寄存器,支持WOL等)。

2、网络接口

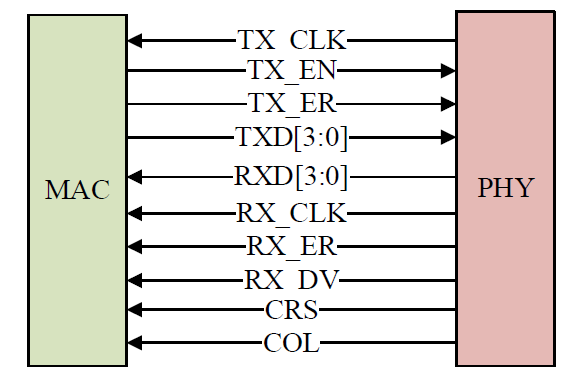

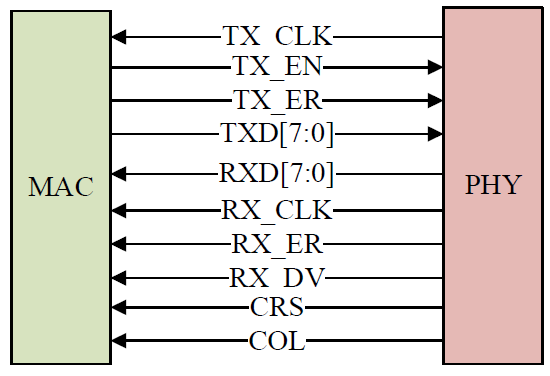

2.1 MII 接口

MII 全称是Media Independent Interface,直译过来就是介质独立接口,它是IEEE-802.3 定

义的以太网标准接口,MII 接口用于以太网MAC 连接PHY 芯片,连接示意图如图40.1.2.1 所

示:

MII 接口一共有16 根信号线,含义如下:

TX_CLK:发送时钟,如果网速为100M 的话时钟频率为25MHz,10M 网速的话时钟频率

为2.5MHz,此时钟由PHY 产生并发送给MAC。

TX_EN:发送使能信号。

TX_ER:发送错误信号,高电平有效,表示TX_ER 有效期内传输的数据无效。10Mpbs 网

速下TX_ER 不起作用。

TXD[3:0]:发送数据信号线,一共4 根。

RXD[3:0]:接收数据信号线,一共4 根。

RX_CLK:接收时钟信号,如果网速为100M 的话时钟频率为25MHz,10M 网速的话时钟

频率为2.5MHz,RX_CLK 也是由PHY 产生的。

RX_ER:接收错误信号,高电平有效,表示RX_ER 有效期内传输的数据无效。10Mpbs 网

速下RX_ER 不起作用。

RX_DV:接收数据有效,作用类似TX_EN。

CRS:载波侦听信号。

COL:冲突检测信号。

MII 接口的缺点就是所需信号线太多,这还没有算MDIO 和MDC 这两根管理接口的数据

线,因此MII 接口使用已经越来越少了。

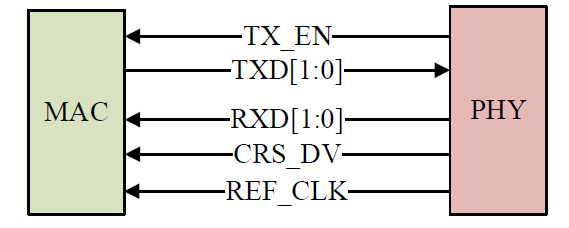

2.2 RMII 接口

RMII 全称是Reduced Media Independent Interface,翻译过来就是精简的介质独立接口,也

就是MII 接口的精简版本。RMII 接口只需要7 根数据线,相比MII 直接减少了9 根,极大的

方便了板子布线,RMII 接口连接PHY 芯片的示意图如图40.1.2.2 所示:

TX_EN:发送使能信号。

TXD[1:0]:发送数据信号线,一共2 根。

RXD[1:0]:接收数据信号线,一共2 根。

CRS_DV:相当于MII 接口中的RX_DV 和CRS 这两个信号的混合。

REF_CLK:参考时钟,由外部时钟源提供,频率为50MHz。这里与MII 不同,MII 的接

收和发送时钟是独立分开的,而且都是由PHY 芯片提供的。

2.3 GMII 接口

GMII(Gigabit Media Independant Interface),千兆MII 接口。GMII 采用8 位接口数据,工

作时钟125MHz,因此传输速率可达1000Mbps;同时兼容MII 所规定的10/100Mbps 工作方式。

GMII 接口数据结构符合IEEE 以太网标准,该接口定义见IEEE 802.3-2000。信号定义如下:

GTX_CLK:1000M 工作模式下的发送时钟(125MHz)。

TX_EN:发送使能信号。

TX_ER:发送错误信号,高电平有效,表示TX_ER 有效期内传输的数据无效。

TXD[7:0]:发送数据信号线,一共8 根。

RXD[7:0]:接收数据信号线,一共8 根。

RX_CLK:接收时钟信号。

RX_ER:接收错误信号,高电平有效,表示RX_ER 有效期内传输的数据无效。

RX_DV:接收数据有效,作用类似TX_EN。

CRS:载波侦听信号。

COL:冲突检测信号。

与MII 接口相比,GMII 的数据宽度由4 位变为8 位,GMII 接口中的控制信号如TX_ER、

TX_EN、RX_ER、RX_DV、CRS 和COL 的作用同MII 接口中的一样,发送参考时钟GTX_CLK

和接收参考时钟RX_CLK 的频率均为125MHz(在1000Mbps 工作模式下)。

在实际应用中,绝大多数GMII 接口都是兼容MII 接口的,所以,一般的GMII 接口都有两个发送参考时钟:TX_CLK 和GTX_CLK(两者的方向是不一样的,前面已经说过了),在用作

MII 模式时,使用TX_CLK 和8 根数据线中的4 根。

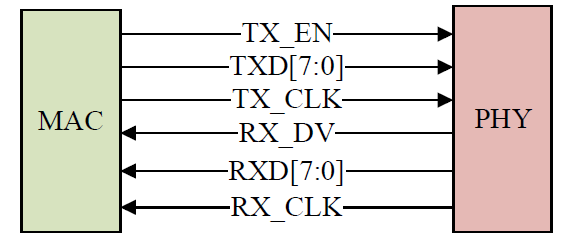

2.4 RGMII 接口

RGMII(Reduced Gigabit Media Independant Interface),精简版GMII 接口。将接口信号线数量

从24 根减少到14 根(COL/CRS 端口状态指示信号,这里没有画出),时钟频率仍旧为125MHz,

TX/RX 数据宽度从8 为变为4 位,为了保持1000Mbps 的传输速率不变,RGMII 接口在时钟的

上升沿和下降沿都采样数据,在参考时钟的上升沿发送GMII 接口中的TXD[3:0]/RXD[3:0],在

参考时钟的下降沿发送GMII 接口中的TXD[7:4]/RXD[7:4]。RGMII 同时也兼容100Mbps 和

10Mbps 两种速率,此时参考时钟速率分别为25MHz 和2.5MHz。

TX_EN 信号线上传送TX_EN 和TX_ER 两种信息,在TX_CLK 的上升沿发送TX_EN,下

降沿发送TX_ER;同样的,RX_DV 信号线上也传送RX_DV 和RX_ER 两种信息,在RX_CLK

的上升沿发送RX_DV,下降沿发送RX_ER。

RGMII 接口定义如下所示:

关于这些接口定义相关的内容我们就讲到这里了,除了上面说到4 种接口以外,还有其他

接口,比如SMII、SSMII 和SGMII 等,关于其他接口基本都是大同小异的,这里就不做讲解

了。正点原子的ATK-DLRK3568 开发板上的网口是采用RGMII 接口来连接MAC 与外部PHY

芯片。

2.5 MDIO 接口

MDIO 全称是Management Data Input/Output,直译过来就是管理数据输入输出接口,是一

个简单的两线串行接口,一根MDIO 数据线,一根MDC 时钟线。驱动程序可以通过MDIO 和

MDC 这两根线访问PHY 芯片的任意一个寄存器。MDIO 接口支持多达32 个PHY。同一时刻

内只能对一个PHY 进行操作,那么如何区分这32 个PHY 芯片呢?和IIC 一样,使用器件地址

即可。同一MDIO 接口下的所有PHY 芯片,其器件地址不能冲突,必须保证唯一,具体器件

地址值要查阅相应的PHY 数据手册。

因此,MAC 和外部PHY 芯片进行连接的时候主要是MII/RMII(百兆网)或GMII/RGMII

(千兆网)和MDIO 接口,另外可能还需要复位、中断等其他引脚。

openvela 操作系统专为 AIoT 领域量身定制,以轻量化、标准兼容、安全性和高度可扩展性为核心特点。openvela 以其卓越的技术优势,已成为众多物联网设备和 AI 硬件的技术首选,涵盖了智能手表、运动手环、智能音箱、耳机、智能家居设备以及机器人等多个领域。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)