嵌入式系统设计原理(24h系列)

嵌入式系统设计原理,这门课可以参考书后每章节的课后题,课后题答案我在文章中给出了一些,需要学习的语言如第二章所示,要进行练习。

第一章

嵌入式系统:任何包含可编程计算机,但其本身不是通用计算机的设备。

Eg

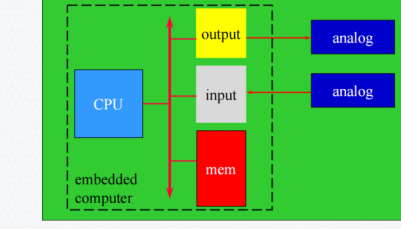

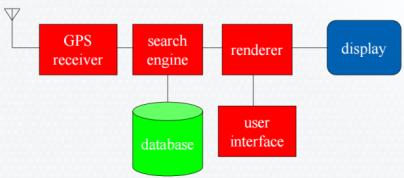

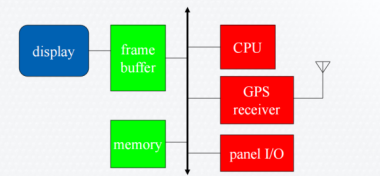

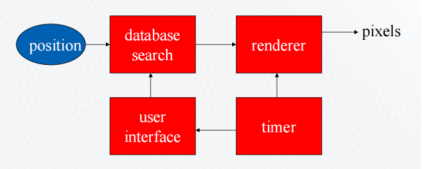

嵌入式计算系统的本质:在资源受限的条件下,通过CPU、内存和I/O设备在总线上的协同工作,实现对特定任务的实时控制和处理。

嵌入式系统的特征:

- 功能复杂:复杂的算法和用户接口

- 实时性:操作必须在规定时限内完成

硬实时:错过规定时限产生系统错误;软实时:错过规定时限降低系统性能。多速率

- 低制造成本

- 低功耗

- 人少效率高的开发队伍

嵌入式系统相关的技术:信息处理技术,网络互联技术,嵌入技术,SoC设计技术,嵌入式操作系统,嵌入式应用软件。

1970s第一个微处理器Intel的4004芯片。

嵌入式系统设计方法:同时采用两种

自顶向下:从系统抽象层开始描述,一步步推进到细节内容。

自底向上:从构成系统的最小组件开始,一步步推进到整个大系统。

(在同一层逐步细化:分析analyze细化refine验证verify)

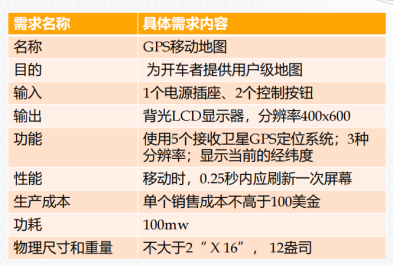

需求分析:用平常的文字将用户需要什么,期望得到什么描写出来

功能需求:系统输出作为系统输入的函数

非功能需求:1性能2成本3物理尺寸及重量4能耗5可靠性

需求分析表:1名称2目的3输入4输出5功能6性能7生产成本8功耗9物理尺寸和重量

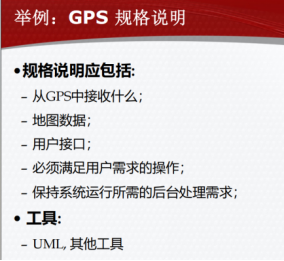

规格说明是更精确的描述系统要做什么,可能包括功能性和非功能部分,规格说明的形式可能是可执行的,也可以用数学形式化方法表述。

体系结构:描述应该采用什么样的部件满足系统的规格说明(硬件,软件,必须注意规格说明中的功能性及非功能性规格说明)

需求是客户想实现的目标,非正式化描述,而规格说明是针对需求整理后包含充足信息的文档。需求->规格说明==客户语言->设计者语言

规格说明只描述系统如何工作,不涉及如何实现,是需求分析的细化,可能包括功/非功。体系结构描述系统如何实现,系统内部详细构造,指导各组件设计,必须注意规格说明中的功/非功。

嵌入式系统设计的问题与挑战

系统集成可能会有许多问题,尽可能在集成之前,对每一个模块或子系统进行测试。

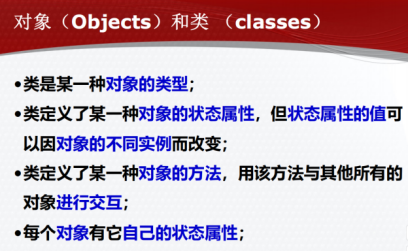

UML是由Booch et al等人开发成功的建模语言;目的:采用面向对象的建模思路、可视化特性、适合于不同抽象层次系统的建模、能提供设计需要的所有功能

类名-属性-方法

连接Link定义了两个对象之间的包含关系。—

关联associations定义了两个类之间的包含关系0..*—1

嵌入式系统结构描述方法:UML对象、UML类、派生类、单重继承/多重继承、连接/关联

嵌入式系统行为描述方法:基于事件驱动的状态机、事件、顺序图。

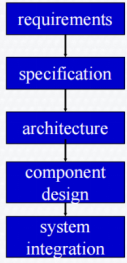

需求分析->(概要详细设计->详细规格设计)->结构设计->软硬件系统设计->系统集成

第二章

计算机体系结构分类: 1字节=8位 一字=4字节

冯诺依曼:一个存储器存区域同时存储数据、指令;中央处理器(CPU)从存储器中取指令。CPU内部寄存器有PC(程序计数器),IR(指令寄存器),通用寄存器。

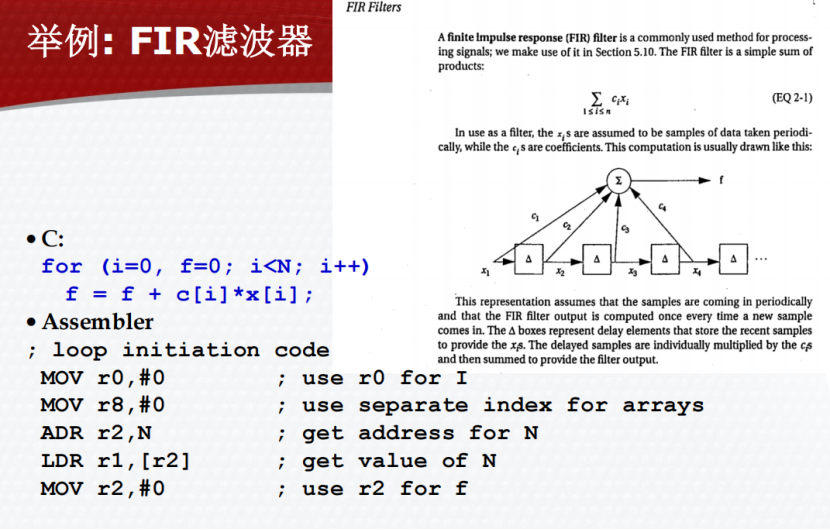

哈佛:哈佛程序结构不能进行自修改,哈佛结构同时支持并发两个端口操作(eg,一个端口处理数据,一个端口处理程序),大部分的DSPs(数字信号处理器)都用哈佛结构来处理流数据。原因是:1-提供较大存储带宽哈佛结构中,指令和数据使用不同的存储和总线,这使得系统可以同时进行指令获取和数据读取/写入。通过同时访问两个端口,系统能够提供 更高的带宽,以便处理更大量的流数据。2-提供更多可预见带宽存储分离,指令和数据的访问不会相互竞争,避免了带宽冲突。因此,处理器可以更容易地预测存储带宽的使用情况,并为实时数据流提供可靠的处理能力。

CISC复杂指令集计算机:许多地址寻址模式、许多操作数提供复杂的指令来减少程序的指令数,提高编程效率

RISC简化指令集计算机:load/store指令、流水线指令减少指令的复杂性来提高执行效率,使每条指令的执行时间较短。

嵌入式微处理器分类:嵌入式微处理器(EMPU),微控制器(Microcontroller),数字信号处理器(DSP),片上系统(SoC)

Intel8051微控制器—寻址空间大,模块化结构,指令集完善,集成多种中断源,开发环境要求低

大端:数据的高位字节存在低地址处,/网络协议

小端:数据的低位字节存在低地址处,/个人电脑

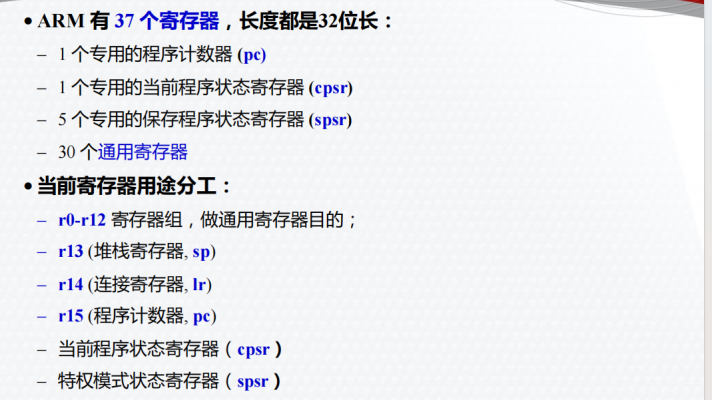

ARM处理器(RISC),32位体系结构,支持数据宽度8/16/32位,大部分实现2个指令集系统:

32位ARM指令集,16位压缩指令集(Thumb)。Jazelle核可执行Java代码

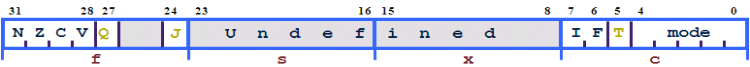

CPSR前四位:

当二进制补码运算结果为负,负位(N)被设置为1

当结果的每一位都为0时,零位(Z)被设置为1

当计算有进位时,进位(C)被设置为1

当算术运算结果溢出时,溢出位(V)被设置为1

Q位:粘性溢出,直到复位都保持状态

J位:jazelle位,当J位被设置为1时,表示处理器处于Jazelle状态,允许ARM处理器运行Java字节码

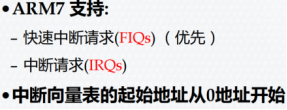

中断取消标识:I位: 中断请求(IRQ)禁用位。当I位设置为1时,处理器禁用普通中断请求:即使有中断请求,处理器也不会响应

F 位: 快速中断请求(FIQ)禁用位。当F位设置为1时,处理器会禁用快速中断请求。意味着处理器不会响应快速中断请求

T位:T = 0: 处理器处于ARM状态,处理32位的ARM指令;T = 1: 处理器处于Thumb状态,Thumb是一个16位的指令集

程序计数器pc不同工作方式:ARM-32bit-字;Thumb-16bit-半字;Jazelle-8bit-微处理器每次读4条指令形成一个字

PC保存在哪?ARM所有指令都32位且需按字操作,pc存于[31:2]位,[1:0]位未定义

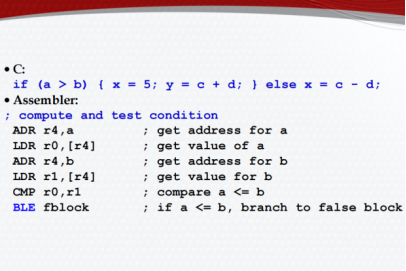

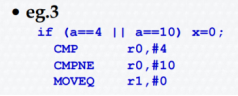

比较:CMP下面

接MOVEQ(相等立即数或寄存器值移到存储器)MOVET(不等)后放前

接BLE:branch if less or equal 前

后跳转,BEQ:前=后跳转 BNE不等跳转

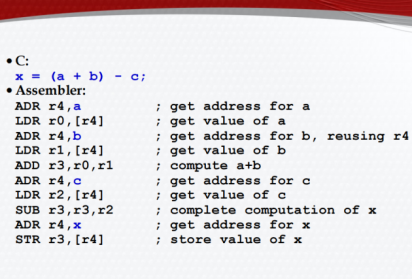

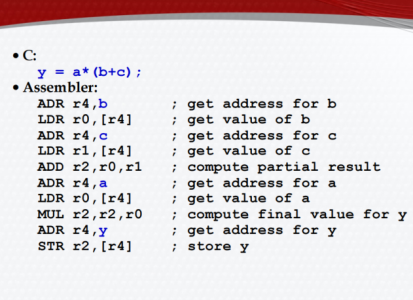

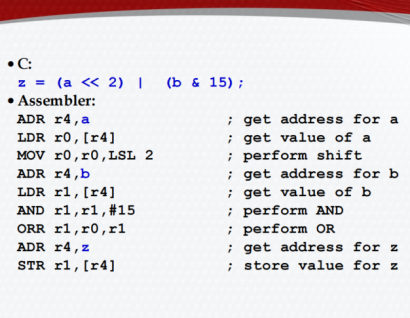

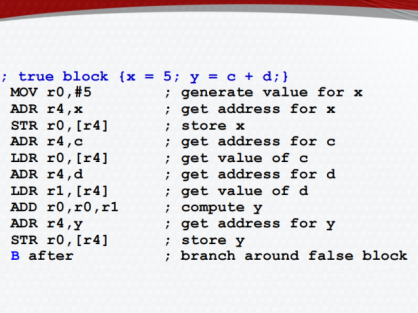

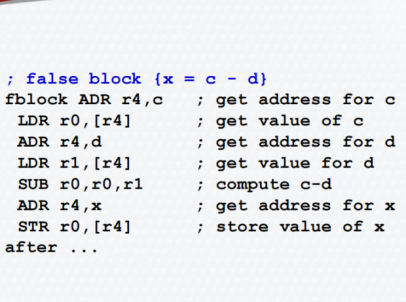

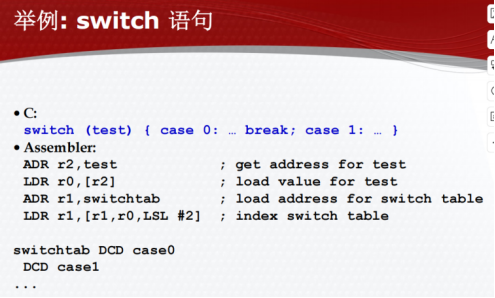

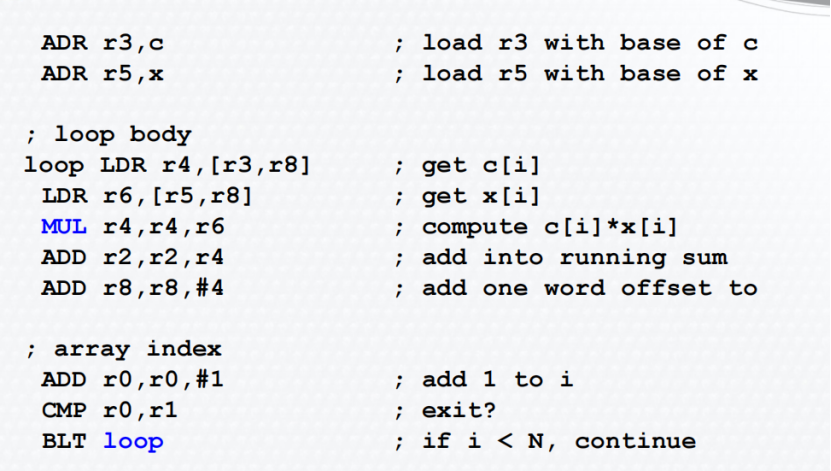

ADD r3,r1,r2 ;r3=r1+r2 SUB r3,r3,r2;r3=r3-r2 MUL乘

ADR r4,a ;r4为a的地址

LDR r0,[r4] ;r0=a

STR r3,[r4] ;把r3的值存在r4地址 1+2/1+3

第三章

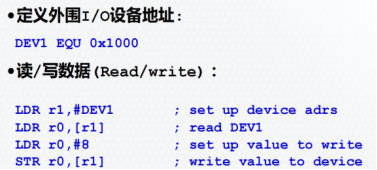

I/O设备通常包括一些模拟元件或非电子元件,与CPU的关系通过数字接口进行控制

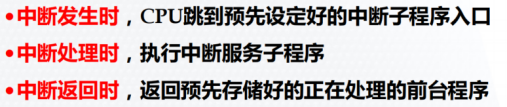

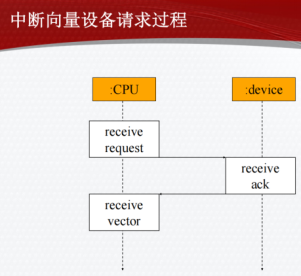

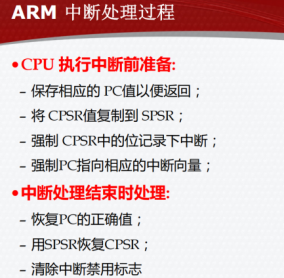

中断请求—中断确认—中断处理程序—中断向量和优先级—中断机制和队列—中断开销

为什么大多数程序使用中断方式驱动I/O而不是忙等待方式?P75

忙等待:1、效率较低2、CPU在处理I/O时不能同时处理其他工作3、并发I/O处理困难

中断:1、CPU可通过中断方式改变外围设备的控制流2、产生中断程序对I/O设备进行控制

中断机制:I/O发送中断请求,CPU发送中断应答,CPU读取I/O的状态寄存器和数据寄存器,以确定中断的原因,并执行相应的中断服务程序来处理中断。

CPU与外设通过CPU总线相连。

响应中断的最坏情况延时为27时钟周期:2个周期用来同步外部请求;最多20个周期来完成当前指令 ;3个周期让数据异常终止 ;2个周期用来进入中断处理程序

概念及作用:管态4;异常3;陷阱[软中断]2ARM提供SWI专门指令;

协处理器:增加了一个特殊功能的硬件单元,ARM最多支持16个协处理器eg浮点运算单元

高速缓存cache:

替换策略:随机策略,最近最少使用策略

平均内存访问时间tav;高速缓存访问时间tcache;主内存访问时间tmain;命中率h

tav=htcache+(1-h)tmain

直接映射(通写,回写),组相联映射见作业题。

如何实现虚拟存储:内存管理单元设计;地址转换;内存组织体系

计算机内存管理中的两种主要组织方式:段和页

影响CPU性能的因素:CPU时钟频率,CPU指令流水线,CPUcache

指令流水线:CPU同时执行几条指令,这些指令处于不同执行阶段

ARM、SHARC 都是 3阶段的指令流水线:取指令,译码,执行(图)

性能提升:不产生指令延时的基础上,提高吞吐量

为什么从睡眠节能状态返回和从空闲节能状态返回不能使用相同的机制?

第四章

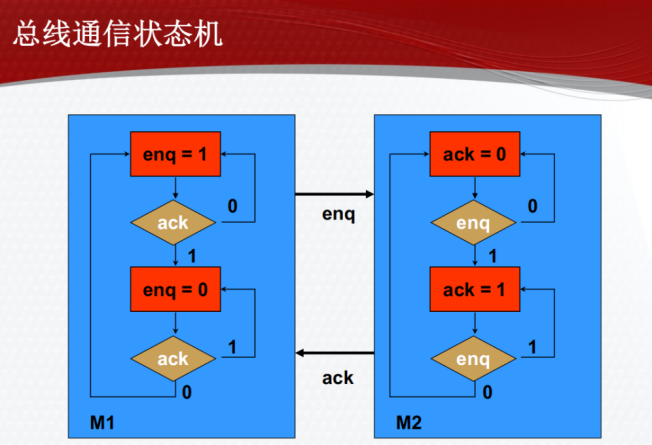

四次握手协议中的设备1和设备2状态图(上图)

总线信号通常为三态

地址线、数据线一般采用多路复用技术

连接在总线上的每个设备都应满足最大总线驱动能力

总线通常包括时钟信号。

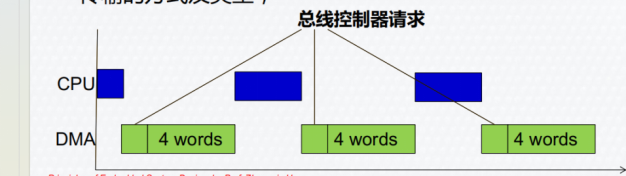

直接存储器访问(DMA)DMA在无需CPU控制的情况下,对总线进行高速读写的控制机制

CPU启动DMA传输 (展现DMA操作的时序图)(上图)

总线控制器可以直接控制总线操作,通常默认为CPU。

存储器类型:ROM只读,RAM读写(DRAM\SRAM)

S静态:更快、更容易与逻辑集成、更高功耗;D动态:更密集、必须刷新。

FLASH的类型:NOR、NAND,寿命是可以写1百万次

为DRAM刷新操作的读事物绘制时序图Q4-22.

I/O设备中的定时器和计数器都采用中断处理,但定时器的输入为周期性信号eg.watchdog;计数器的输入信号为异步、偶然产生的信号。

消去多次颤动:硬件使用单步定时器,软件采用定时扫描的办法。

通信接口总线中USB串行是主从设备,易于使用\低成本\传输速度高\实时音频视频应用\同步异步通信

每种USB逻辑设备是一类端点设备集合;每类端点设备是一个简单的数据源

帧:传输一个时间片数据,称为一个帧;开始包SOF

传输类型(4):控制传输、批量传输、中断传输、等时传输

SoC是一种将传统计算机或其他电子系统中的多个组件集成到单个集成电路(芯片)上的技术。

openvela 操作系统专为 AIoT 领域量身定制,以轻量化、标准兼容、安全性和高度可扩展性为核心特点。openvela 以其卓越的技术优势,已成为众多物联网设备和 AI 硬件的技术首选,涵盖了智能手表、运动手环、智能音箱、耳机、智能家居设备以及机器人等多个领域。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)