《计算机嵌入式系统》第二章考点解析

微程序设计:将指令分解为多个微操作,每个微操作由微指令实现,多条微指令组成微程序存储在ROM中。执行指令时,逐条读取微指令完成操作。层次模型:硬件层:逻辑电路(如CPU、存储器)。微程序层:通过微指令实现指令功能(如加法指令分解为取数、运算、存结果等微操作)。指令系统层:程序员可见的机器指令集合(如汇编指令对应的机器码)。操作系统层/语言处理层:软件抽象层(如OS管理硬件、编译器翻译高级语言)。微

2.1 计算机系统的基本结构与组成——微程序设计思想(理解)

核心概念

-

微程序设计:将指令分解为多个微操作,每个微操作由微指令实现,多条微指令组成微程序存储在ROM中。执行指令时,逐条读取微指令完成操作。

-

层次模型:

-

硬件层:逻辑电路(如CPU、存储器)。

-

微程序层:通过微指令实现指令功能(如加法指令分解为取数、运算、存结果等微操作)。

-

指令系统层:程序员可见的机器指令集合(如汇编指令对应的机器码)。

-

操作系统层/语言处理层:软件抽象层(如OS管理硬件、编译器翻译高级语言)。

关键原理

-

微程序 vs. 硬连线控制器:

-

微程序控制器:通过微指令序列实现复杂指令,硬件结构简单但执行速度较慢(如早期CISC处理器)。

-

硬连线控制器:直接用逻辑电路生成控制信号,速度快但设计复杂(如RISC处理器)。

-

CISC与RISC的设计差异:

-

CISC依赖微程序,指令功能复杂(如VAX-11/780有330条指令);

-

RISC摒弃微程序,指令简单且数量少(如MIPS仅几十条指令)。

2.2 模型机存储器子系统——分级设计、端格式与字对齐(理解/了解)

1. 存储器分级设计(理解)

-

目标:平衡速度、容量、成本,构建分层存储体系:

-

寄存器:最快,容量最小(CPU内部,如累加器ACC)。

-

高速缓存(Cache):次快,容量较小(SRAM,存储CPU常用数据/指令)。

-

主存(内存):速度中等,容量中等(DRAM,程序运行空间)。

-

外存(辅存):最慢,容量最大(如磁盘、SSD,非易失性存储)。

-

典型结构:

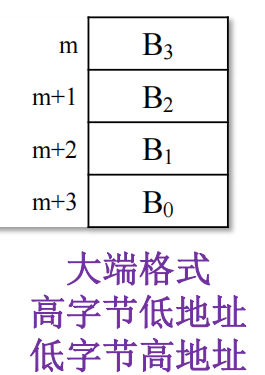

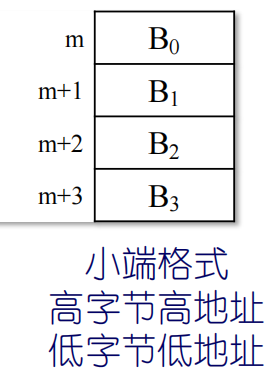

CPU ↔ Cache ↔ 主存 ↔ 外存 (速度递减,容量递增)2. 小端与大端格式(了解)

-

定义:

-

小端(Little-Endian):低字节存低地址,高字节存高地址(如Intel x86)。

-

例:32位数据

0x12345678存储为:[0x78][0x56][0x34][0x12](地址递增方向)。 -

大端(Big-Endian):高字节存低地址,低字节存高地址(如Motorola处理器)。

-

例:同上数据存储为:

[0x12][0x34][0x56][0x78]。 -

影响:字节顺序影响多字节数据解析(如网络传输需统一格式)。

3. 字长与字对齐(了解)

-

字长:计算机一次处理的二进制位数(如32位机字长4字节)。

-

对齐规则:

-

16位机:字地址为2的倍数;

-

32位机:字地址为4的倍数;

-

目的:确保CPU一次总线操作读取完整字,提高存取效率(如Intel 8086通过

BHE和A0信号选择存储体)。2.4 模型机指令集与执行流程——指令执行、汇编与流水线(掌握)

1. 指令执行流程(结合汇编与寻址)

-

典型步骤:

-

取指(Fetch):PC指向指令地址,从内存读取指令到IR(指令寄存器)。

-

译码(Decode):ID(指令译码器)解析操作码,确定指令功能(如加法、跳转)。

-

取操作数(Read):根据寻址方式获取操作数(如寄存器寻址

MOV R0, #0x1234)。 -

执行(Execute):ALU完成运算或控制部件调整PC(如条件跳转

JO L2)。 -

回写(Writeback):结果写入寄存器或内存(如

STR R1, [R3+0x80])。

-

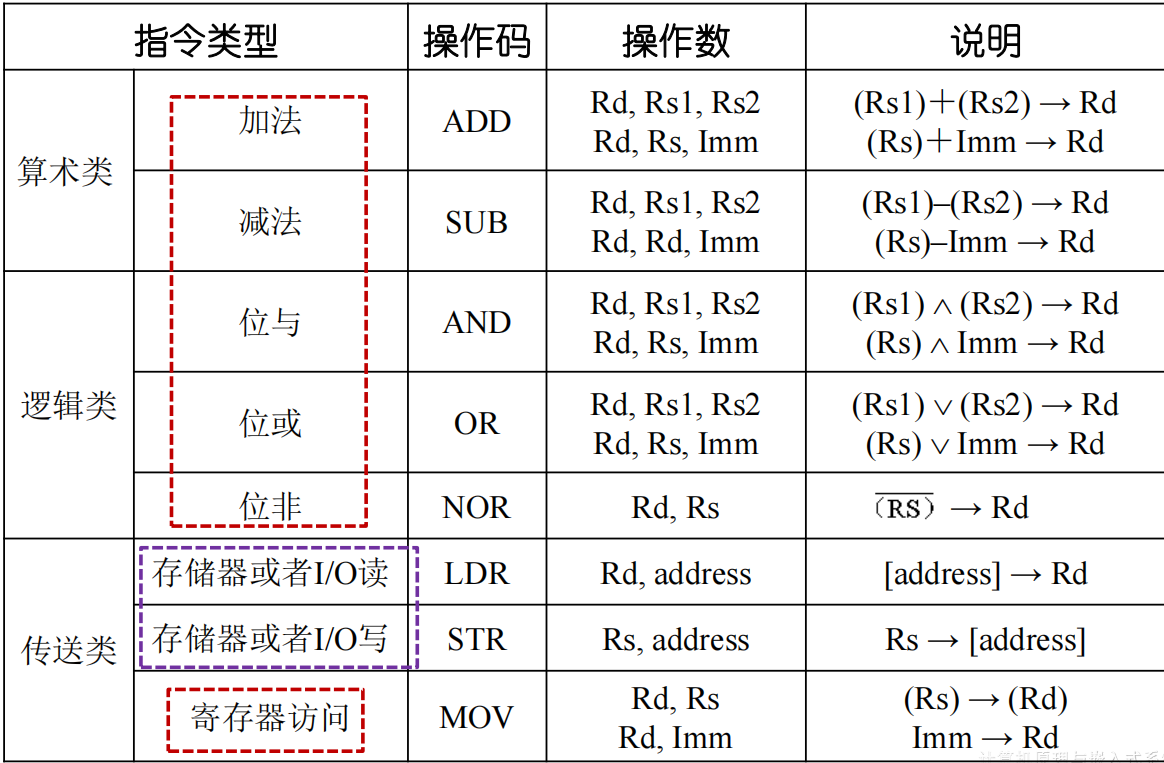

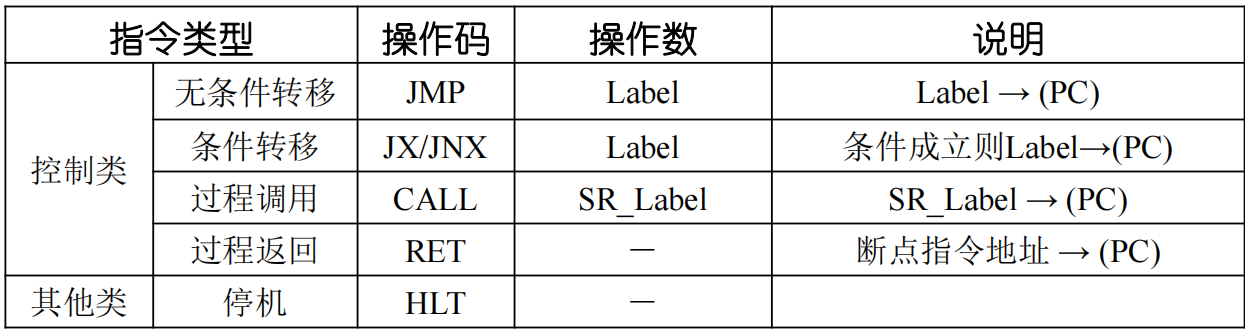

汇编示例(模型机指令):

START: MOV R0, #0x000FF000 ; 立即数送R0(取指→译码→回写) LDR R1, [R3] ; 寄存器间接寻址取内存数据(取指→译码→取操作数→回写) ADD R1, R0, R1 ; 寄存器寻址加法(取指→译码→执行→回写) JO L2 ; 条件跳转(取指→译码→执行:检测标志位) STR R1, [R3+#0x80] ; 基址+偏移量寻址存结果(取指→译码→取操作数→回写) L2: HLT ; 停机(取指→执行)2. 流水线原理(掌握)

-

三级流水线:取指(IF)、译码(ID)、执行(EX)。

-

五级流水线:取指(IF)、译码(ID)、执行(EX)、访存(MEM)、回写(WB)。

-

流水线时空图:

周期 1 2 3 4 5 6 7 指令1 IF ID EX MEM WB 指令2 IF ID EX MEM WB 指令3 IF ID EX MEM WB -

三种相关冲突及解决:

- 资源相关:多条指令争用同一部件(如冯诺依曼结构取指与访存冲突)。

-

解决:

哈佛结构(指令/数据分存,解除存取操作数和取指之间的资源相关,使取指和数据访问可同时进行)

插入气泡(停顿流水线,后等前)。

-

数据相关:后指令依赖前指令结果

(如

ADD R1, R0, R2后接AND R3, R1, R4)。

-

解决:

插入气泡

数据旁路(定向推送,设置专用通道,前一条指令执行结果通过专用通道直接推送给下一条指令,不用非要等到上一个指令执行完)

指令调度(优化编译器,检查前后指令,调整执行顺序,使冲突指令距离拉开)。

- 控制相关:跳转指令导致流水线断流(如条件跳转

JO L2需排空后续指令)。

-

解决:

动态转移预测(根据过去的行为进行预测,对发生转移的可能性加权量化,如BTB缓冲器预测跳转地址)

转移延迟槽技术(转移指令后面的一个时间片称为转移延迟槽,无论是否转移,位于转移延迟槽的指令总是会被执行,可减少转移代价)

3.操作

-

2.5 计算机体系结构改进——RISC/CISC与流水线(掌握/了解)

1. RISC vs. CISC(了解)

特性 CISC RISC 指令数量 多(如x86超百条) 少(如ARM约40条) 指令长度 可变(如8086指令1-6字节) 固定(如MIPS 4字节) 控制器 微程序控制器 硬连线控制器 寻址方式 多样(如寄存器间接、基址变址) 简单(如基址+偏移量) 典型处理器 Intel x86、VAX ARM、MIPS、RISC-V 2. 流水线优化(掌握)

-

超标量技术:多条流水线并行执行多条指令(如Pentium的U/V流水线)。

-

超线程技术:单个物理核心模拟多个逻辑核心,提升多任务效率(如Intel超线程)。

-

多核处理器:单芯片集成多个独立核心(如ARM Cortex-A系列多核),通过缓存一致性协议协同工作。

2.8 计算机性能评测(了解)

核心指标

-

定性指标:

-

字长、存储容量、总线带宽、功耗、可靠性(MTBF/MTTR)。

-

定量指标:

-

速度等

-

基准测试:

-

SPEC CPU:评测整数/浮点性能(如SPECint、SPECfp)。

-

CoreMark:嵌入式系统性能基准(矩阵运算、状态机等)。

-

Geekbench:跨平台CPU/GPU性能测试(整数、浮点、内存带宽)。

-

效率指标:

-

MIPS(百万指令/秒)、FLOPS(浮点运算/秒)、IPC(每周期指令数)。

openvela 操作系统专为 AIoT 领域量身定制,以轻量化、标准兼容、安全性和高度可扩展性为核心特点。openvela 以其卓越的技术优势,已成为众多物联网设备和 AI 硬件的技术首选,涵盖了智能手表、运动手环、智能音箱、耳机、智能家居设备以及机器人等多个领域。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)